عندما قرأت الخبر أول مرة في AnandTech ظننت لوهلة أن هذا ما ترمي إليه AMD فقلت يا للهول أتريد AMD أن تخدعنا وتعطينا نواتين وهما في الحقيقة نواة ونصف !!

ولكن لحسن الحظ اتضح الأمر أنه ليس صحيح

بدأ الأمر عندما نشر Anandtech مقاله الأول حول Bulldozer وهناك أشار لكون AMD تطلق على هذا التصميم على أنه نواتين مندمجتين بشكل قوي أو عميق إن كانت الترجمة أو التعبير صحيح ( two tightly coupled cores ) ففهم Anandtech بداية أن AMD تريد أن تسمي هذا التصميم على أنه ثنائي النُّوى بدلاً من جعله نواة واحدة !!

وهنا وقع الإشكال... فبدلاً من أن تكون النواة تتضمن وحدة حسابات صحيحة وأخرى عائمة، والنواتين تتضمنان وحدتي حسابات صحيحة ووحدتي حسابات عائمة صارت حسب تصميم AMD وفهم AT تؤول لجعل النواتين تتضمنان وحدتي حسابات صحيحة ووحدة واحدة فقط حسابات عائمة !!

ولكن ولله الحمد أن فهم AT كان خاطئاً...

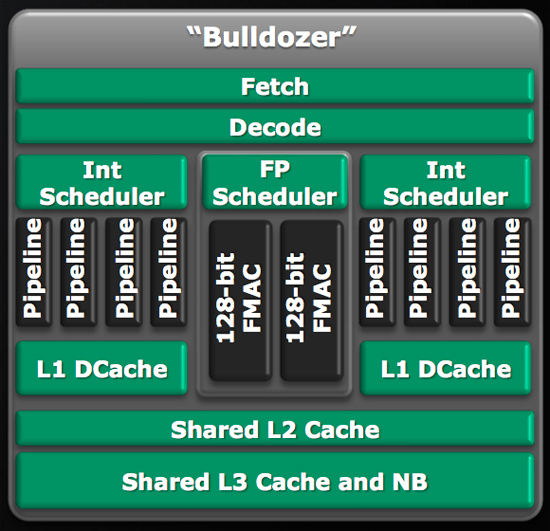

بداية... هذه الصورة تمثلها AMD على أنها Module أو وِحدة بالعربية...

تصف AMD هذه الوِحدة على أنها نواتين متحدتين بشكل عميق أو قوي، وهنا وقع الإشكال حيث ظن AT أن وِحدة واحدة من هذه الوحدات ستشكل معالج ثنائي النُّوى، ووحدتين ستشكلان معالج رباعي النُّوى... ولكن اتضح أن هذا الفهم ليس صحيح...

في سؤال وجهه AT إلى AMD

A few of you wondered how AMD was going to be counting cores in the Bulldozer era; I took your question to AMD via email:

AMD responded:

Anand,

Think of each twin Integer core Bulldozer module as a single unit, so correct.

I took that to mean that my assumption was correct and 4 Bulldozer cores meant 4 Bulldozer modules. It turns out there was a miscommunication and I was wrong. Sorry about that

ترجمته...

بعض منكم تسائل حول كيف ستقوم AMD بحساب الأنوية في عصر Bulldozer: قمت بنقل سؤالكم إلى AMD عن طريق البريد الإلكتروني...

إضافة لذلك، وفقط للتأكد، عندما تشير خارطة الطريق لديكم إلى 4 أنوية Bulldozer من هذه الأنوية

أو هل تعتبر كل واحدة من هذه الأنوية على أنها نواتين... أعتقد أنها الأولى ( المترجم : الأولى تعني أربع أنوية = أربع من تلك الوحدات في الصورة العلوية ) ولكن أود فقط التأكد...

أجابت AMD

أناند. فكر على أساس كل نواتي حسابات صحيحة في وحدة Bulldozer على أنها وحدة واحدة، إذاً ما تعتقده صحيح

أخذت ذلك على أن اعتقادي كان صحيحاً وأن أربع أنوية Bulldozer هي أربع وحدات Bulldozer... اتضح أنه كان يوجد نقص في التواصل وأنني كنت مخطئاً... عذراً على ذلك

خلاصة الأمر، التصميم السابق المسمى بالوحدة والذي يتضمن وحدتي حسابات صحيحة + وحدة حساب فاصلة عائمة هو عبارة عن نواة واحدة بمفهومنا نحن، أي أن معالج Bulldozer المكون من أربع أنوية سيتضمن أربع وحدات من هذه في التصميم أي سيكون المجموع 8 وحدات حساب صحيحة وأربع عائمة قفزاً من 4 حسابات صحيحة و4 عائمة في التصاميم الحالية...

كل وحدة Integer ستبدو على أنها نواة لنظام التشغيل، وبالتالي وحدة واحدة ( تتضمن وحدتي Integer ) ستبدو على أنها نواتين لنظام التشغيل وذلك مثل تقنية Hyper-Threading ولكن الفرق أن HT هي برمجية أكثر من كونها عتادية بينما تقنية AMD هي عتادية أكثر من كونها برمجية لكونها تضع وحدة حساب حقيقية إضافية في النواة...

للمقارنة

تقنية Hyper-Threadin تحتاج لزيادة 5% تقريباً في مساحة النواة وتعطي حتى 30% زيادة في الأداء للتطبيقات التي تدعم تعدد الأنوية

تقنية AMD التي لا نعلم بعد عن اسمها التجاري تحتاج لزيادة تقارب الـ 50% في مساحة النواة ( بدون حساب ذاكرة الكاش ) وتعطي حتى 80% زيادة في الأداء في التطبيقات التي تدعم تعدد الأنوية...

المشكلة أن ذات المقال في Anandtech يطرح إشكالية !!، فبينما السؤال يطرح انطباعاً نتمنى أن يكون صحيحاً نجد أن الصور التوضيحية في الصفحة الثانية تعطي انطباعاً لا نتمنى أن يكون كذلك !!!

فأيهما صحيح الآن ؟؟

المفضلات