AMD تكشف الستار عن خطّتها لمُعالجات AM5 والجيل التالي من Zen 5!

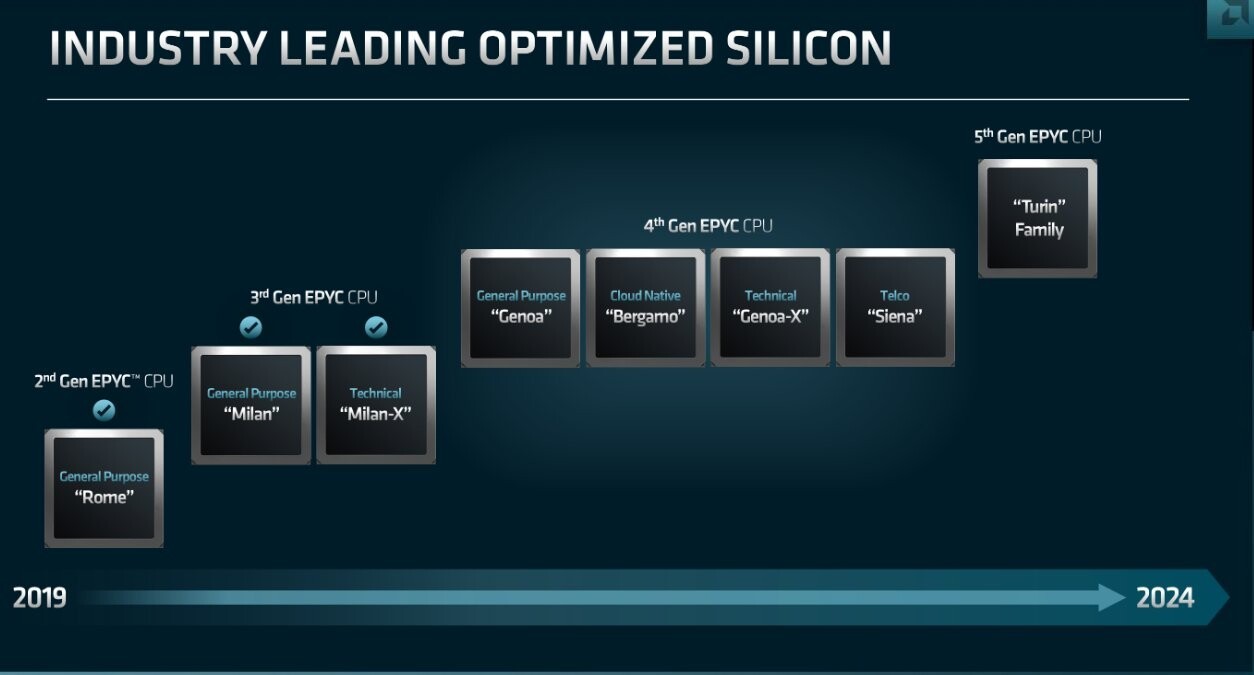

كشفت AMD الأسبوع الماضي عن مجموعة من المعلومات الجديدة بعضها يخص مُعالجات Ryzen القادمة وبعضها يرتبط بمُعالجاتها الرُسوميّة المُرتقبة. فقد كشفت AMD في عرضها التقديمي ليوم المحللين الماليين لعام 2022، النقاب عن الجيل التالي من معمارية "Zen 5". كما وأعلنت عن نيتها لتحديث معالجات CCDs "Zen 4" مع ذاكرة التخزين المؤقت ثلاثية الأبعاد (3DV Cache). كما ستكون هُناك متغيرات من معالجات EPYC "Genoa" مع 3DV Cache، إلى جانب المُعالجات الأساسية منها.

مُعالجات Zen 5 ستُبنى على دقّة تصنيع 4nm

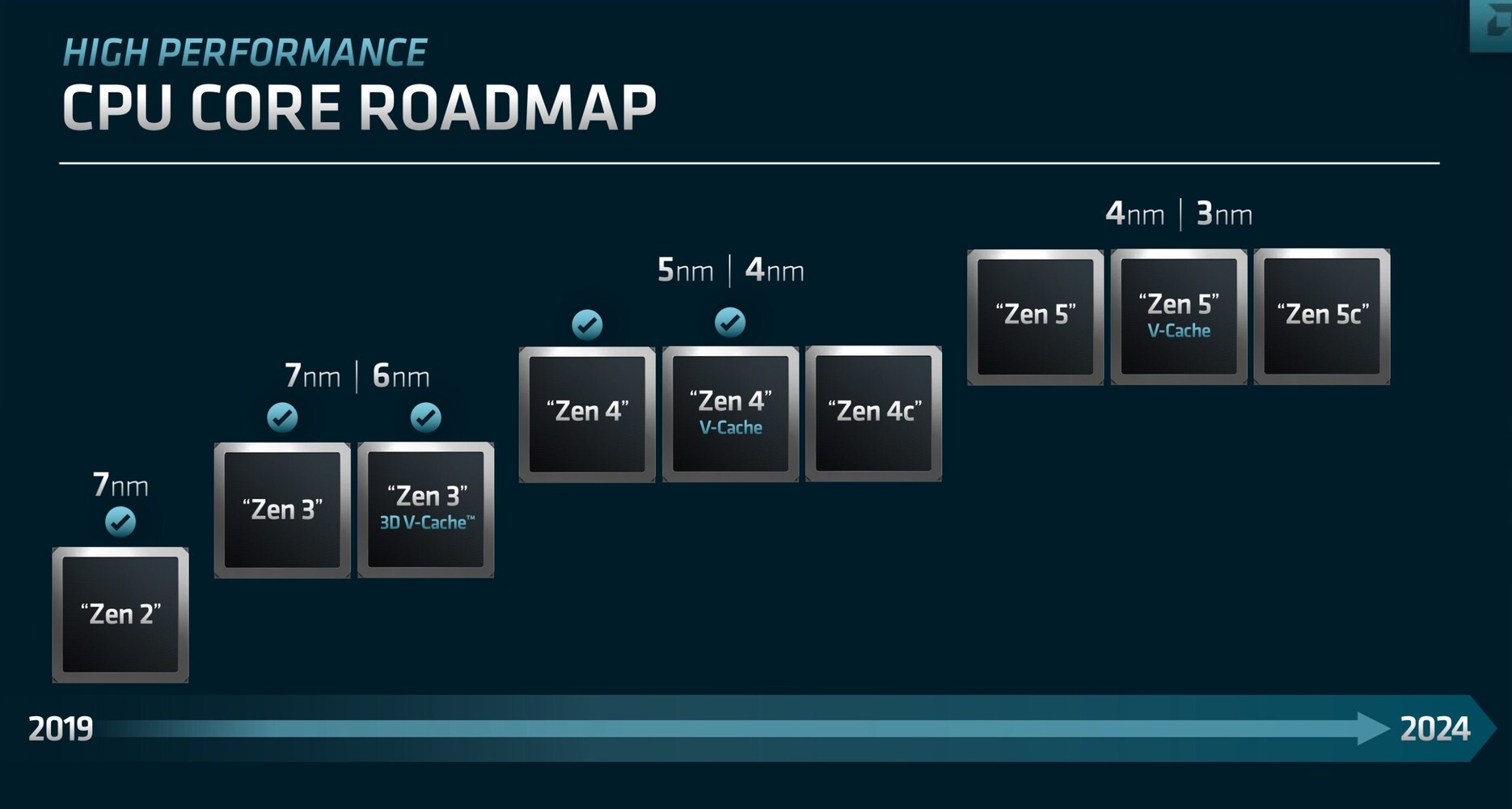

ستظهر بنية "Zen 4" الجديدة لأول مرة بدقّة تصنيع 5 نانومتر (TSMC N5)، ويمكن أن نراها بعد ذلك بتحديث لعُقدة 4 نانومتر الأحدث في وقتٍ ما، على الرغم من أن AMD لم تُحدد ما إذا كان ذلك سيكون من نصيب أي نوع من المُعالجات والفئات. وفي المُقابل، ستظهر بنية "Zen 5" من الجيل التالي لأول بدقة تصنيع 4 نانومتر، وستشهد انكماشًا إلى 3 نانومتر في بعض المنتجات المستقبلية.

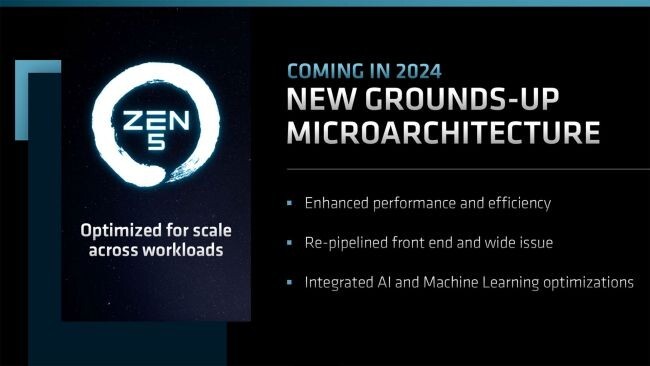

هذا وسيتم تسمية مُعالجات المؤسسات من فئة EPYC المستند إلى معمارية "Zen 5" باسم "Turin". لم تُفصِّل الشركة تفاصيل كثيرة عن المُعالجات، ولكنها قدّمت أول إعلان تشويقي حول ما يُتوقّع رؤيته مع معمارية "Zen 5". ومثل كل جيل معماري من "Zen" آخر قبله، سيُقدِّم "Zen 5" تحسينات في الأداء والكفاءة (زيادة IPC والأداء لكل Watt من الانتقال إلى عقدة التصنيع الجديدة). كما وستقوم AMD بإعادة تصميم الواجهة الأمامية لنواة وحدة المعالجة المركزية، وتُعيد تخطيطها لتشمل تطبيقات أكثر.

تثير AMD أيضًا تحسينات في الذكاء الاصطناعي وتعلّم الآلة AI / ML في الجيل الحالي والقادم. تُلمّح خارطة طريق AMD إلى الظهور لأول مرة عام 2024 لمعالجات "Zen 5" ومعالجات EPYC "Turin". والتي سنرى بعدها العديد من التسميات الأُخرى الخاصّة بقطاعيّ المؤسسات والعملاء، للمنتجات القائمة على معمارية "Zen 5" في الأشهر المقبلة.

الجدير بالذكر أيضاً أن هُناك تكهّنات بأن AMD يمكن أن تعطي "Turin" زيادة في أعداد الأنوية، مع الاحتفاظ بنفس البنية التحتية لحزمة الخدمة SP5؛ مما يعني أنه يمكننا رؤية وحدات CCD أصغر، أو أعداد أنوية أعلى لكل CCD مع "Zen 5".

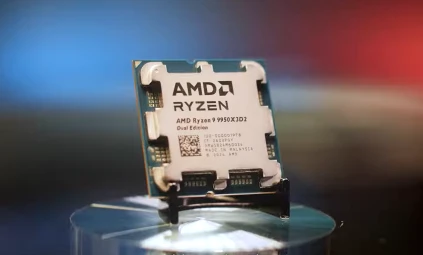

الجيل الثاني من AM5 سيُعرف بـ Granite Ridge

وكما هو الحال مع مُعالجات الجيل الرابع "Raphael"، ستكون مُعالجات الجيل التالي لها وهي "Granite Ridge" هي مُعالجات مكتبية عالية العدد من الأنوية، التي ستتميز بوحدة مُعالجة رُسوميّة مُدمجة iGPU تكفي للمهام المكتبية/الإنتاجية الأساسية، ولكن ليس للألعاب. وأكّدت AMD أيضاً أنها لا ترى "Raphael" كوحدة APU، وأن تعريفها للمُعالجات المُسرّعة "APU" هو أنها مُعالجات تحمل iGPU كبير قادر على تشغيل الألعاب. وستكون وحدات الـAPU التالية للشركة هي "Phoenix Point".

وحدات المُعالجة المُسرّعة Phoenix Point

لا شك أن وحدات المُعالجة المُسرّعة "Phoenix Point" أخذت حظّها الوافر من مطحنة الشائعات منذ شهرين حتى الآن. ويُشاع أنه هذه المُعالجات المُرتقبة ستحتوي على قالب مُترابط مبني على عملية تصنيع TSMC N5 (5 نانومتر)، وستتميّز بوحدات "Zen 4" CCX، ومُعالج رسومي iGPU قوي يعتمد على البنية الرُسوميّة RDNA3 من الجيل التالي، وذاكرة DDR5، وربما PCI-Express Gen 5. هذا ومن المُمكن أن تظهر شريحة السيليكون الجديدة هذه لأول مرة كمُعالجات للحواسيب المحمولة أولاً، ثم تليها بعد ذلك النُسخ المكتبية في حُزْمَة AM5.

الجدير بالذكر أيضاً من العرض التقديمي ليوم التحليل المالي، أن AMD لا تُخطط لتوفير نُسخ من مُعالجات "Rembrandt" إلى منصة AM5، ولكن لا يمكن استبعاد شيء من هذا القبيل لقطاعي Ryzen 3 و Ryzen 5 على الأقل للدخول في هذه الفئة في وقت ما. وللمعلومية، تستخدم مُعالجات "Rembrandt" نسخة أقدم من "Zen 3+" CCX.

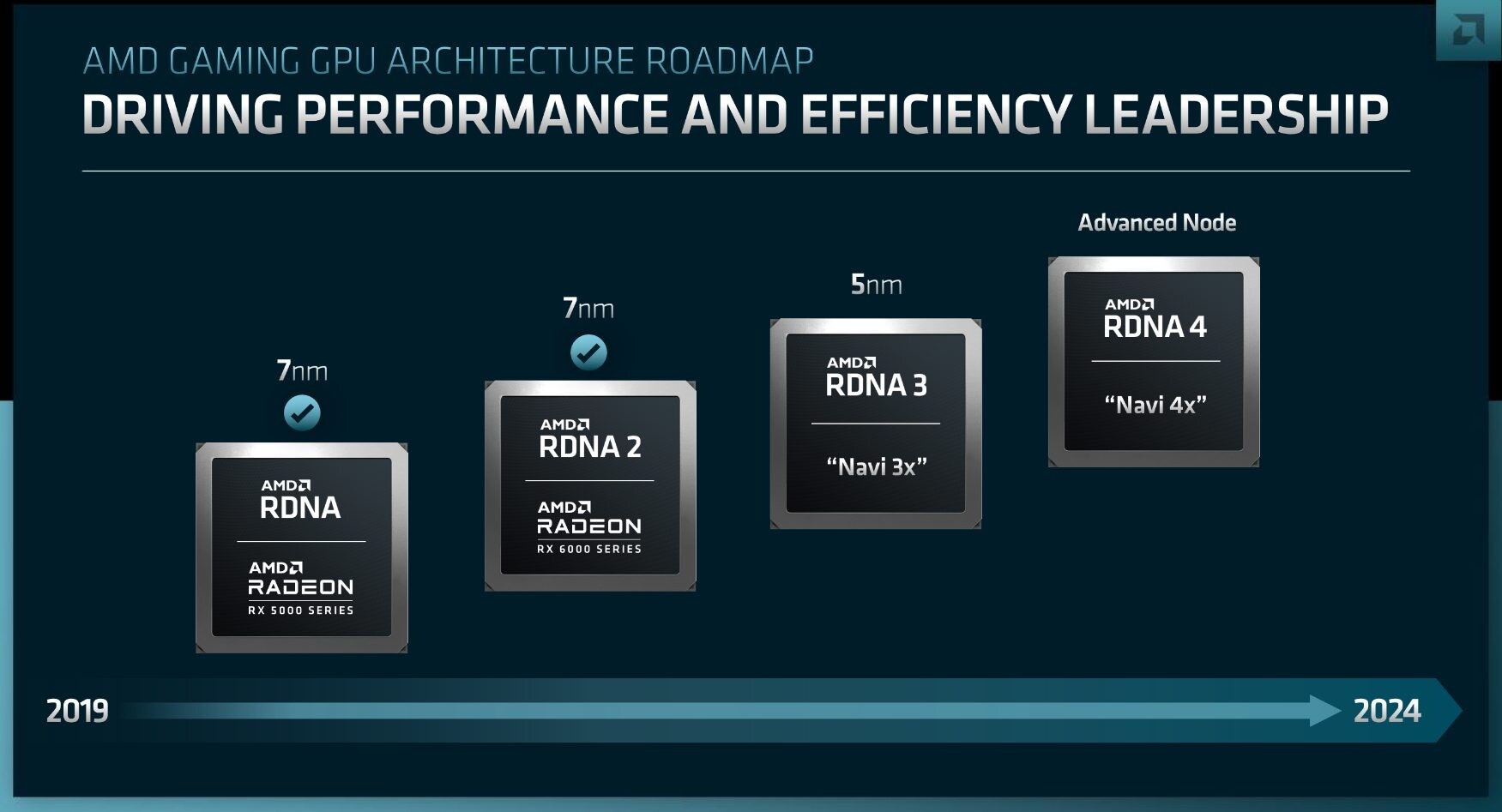

بنية رسومات RDNA3

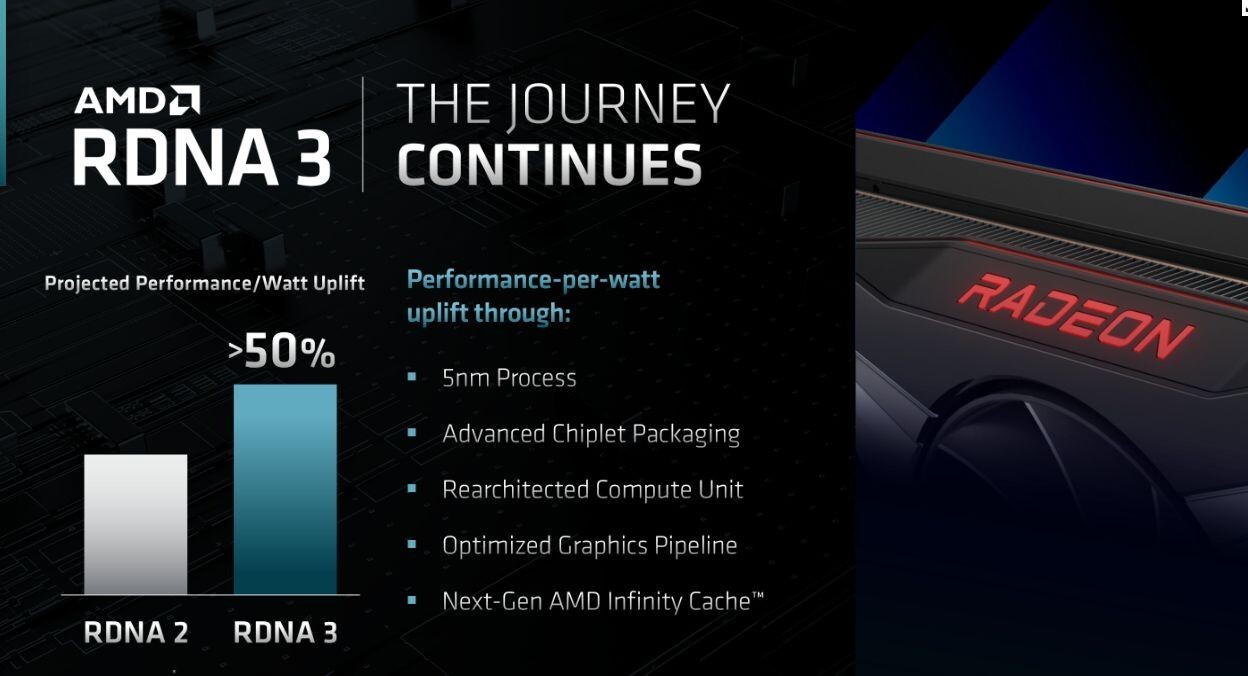

وأخيراً، ادّعت AMD في عرضها التقديمي أيضاً بعض المعلومات المُثيرة الخاصّة ببنيتها الرُسوميّة المُقبلة RDNA3. حيث صرّحت الشركة أنها ستُكرر قفزة الأداء الجيلي التي تزيد عن 50٪ / في الأداء لكل وات مع بنيتها الرُسوميّة RDNA3 القادمة. سيكون هذا تكرارًا للعودة غير المتوقعة إلى قطاعات فئة الأداء العالي من AMD Radeon، والتي حدثت في الجيل الحالي بفضل قفزة الأداء بنسبة 50٪ / وات للبنية الرُسومية RDNA2 مُقابل RDNA. كما وقد قامت الشركة أيضًا بتفصيل واسع للمواصفات الجديدة المختلفة لـ RDNA3 التي ستجعل ذلك ممكنًا.

بادئ ذي بَدْء، ستظهر RDNA3 لأول مرة على عقدة تصنيع السيليكون TSMC N5 (5 نانومتر)، وستظهر لأول مرة نهجًا قائمًا على الرقاقات يُشبه إلى حد ما ما فعلته AMD مع الجيل الثاني من معالجات EPYC "Rome" والجيل الثالث Ryzen "Matisse". ستُشكّل الشرائح المُعبأة بالمُكوّنات المُخصصة للحسابات والمُكوّنات المُخصصة للعرض ثلاثي الأبعاد الشرائح الأساسية أو الـChiplets. في حين أن مكونات الإدخال/الإخراج، مثل وحدات التحكم في الذاكرة، ووحدات التحكم في العرض، ومُحرّكات الوسائط، وما إلى ذلك، سيتم تجميعها في قالب مُنفصل.

كما ذكرت AMD أنها أعادت تصميم الوحدات الحسابية مع RDNA3 لزيادة الـIPC الخاص بها، كما أنها قامت ببعض التغيرات في الأجزاء الخاصّة بالحسابات الهندسية أيضاً. كما وستُضاعف الشركة من استخدام تقنية ذاكرة التخزين المؤقت Infinity Cache on-die، حيث ستتميز معمارية RDNA3 بالجيل التالي من ذاكرة Infinity Cache (والتي تعمل على الأرجح بنطاق ترددي أعلى).

هذا وقد أعلنت الشركة، ولأول مرة، عن بنية رسومات RDNA4 الجديدة. لم تُشارك الشركة أيّة تفاصيل حول RDNA4، إلا أنها ستعتمد على عُقدة تصنيع أكثر تقدمًا من 5 نانومتر. من المتوقع ظهور AMD RDNA3 في النصف الثاني من عام 2022، مع توافرها بشكل عام في عام 2023. وفي المُقابل، من المقرر أن يتم تحديد موعد ظهور RDNA4 ليكون في وقت ما في عام 2024.