شركة AMD تتحدث عن توقعاتها لأنظمة التكديس القادمة

سلطت شركة AMD في عرضها التقديمي في حدث HotChips 33 الضوء على جهود الشركة للبقاء في طليعة تقنية تغليف السيليكون ثلاثية الأبعاد، خاصة وأن شركة Intel المنافسة تخطو خطوات عملاقة مع تقنياتها الجديدة للـ 2.5D و 3D مثل حزم "Ponte Vecchio" و "Sapphire Rapids". وقد كشفت الشركة أنها شاركت في تطوير تقنية تكديس جديدة ورائدة مع شركة TSMC لوحدات الـ CCD القادمة مع معمارية "Zen 3" مع ذواكر مخبئية رأسية ثلاثية الأبعاد.

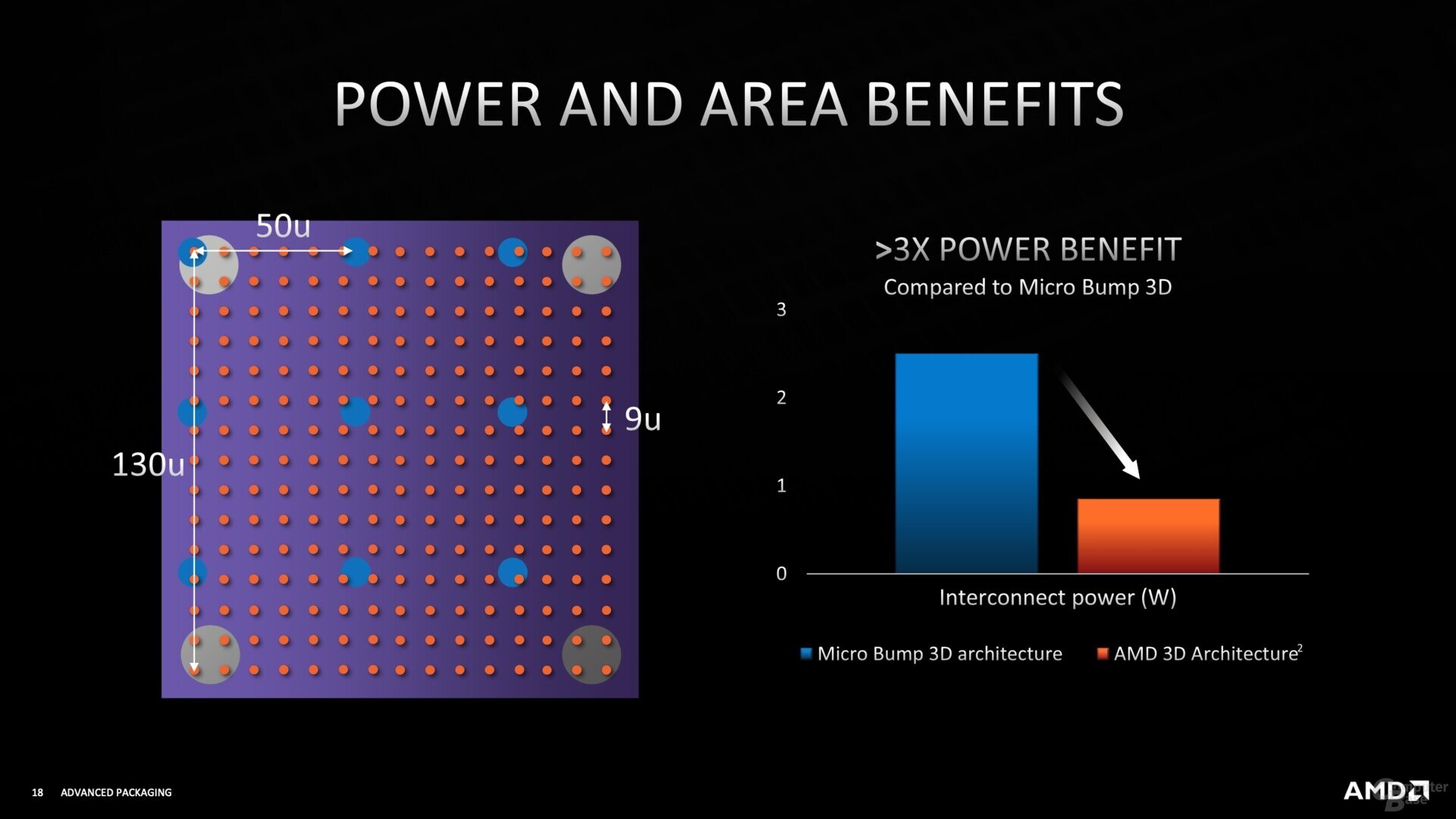

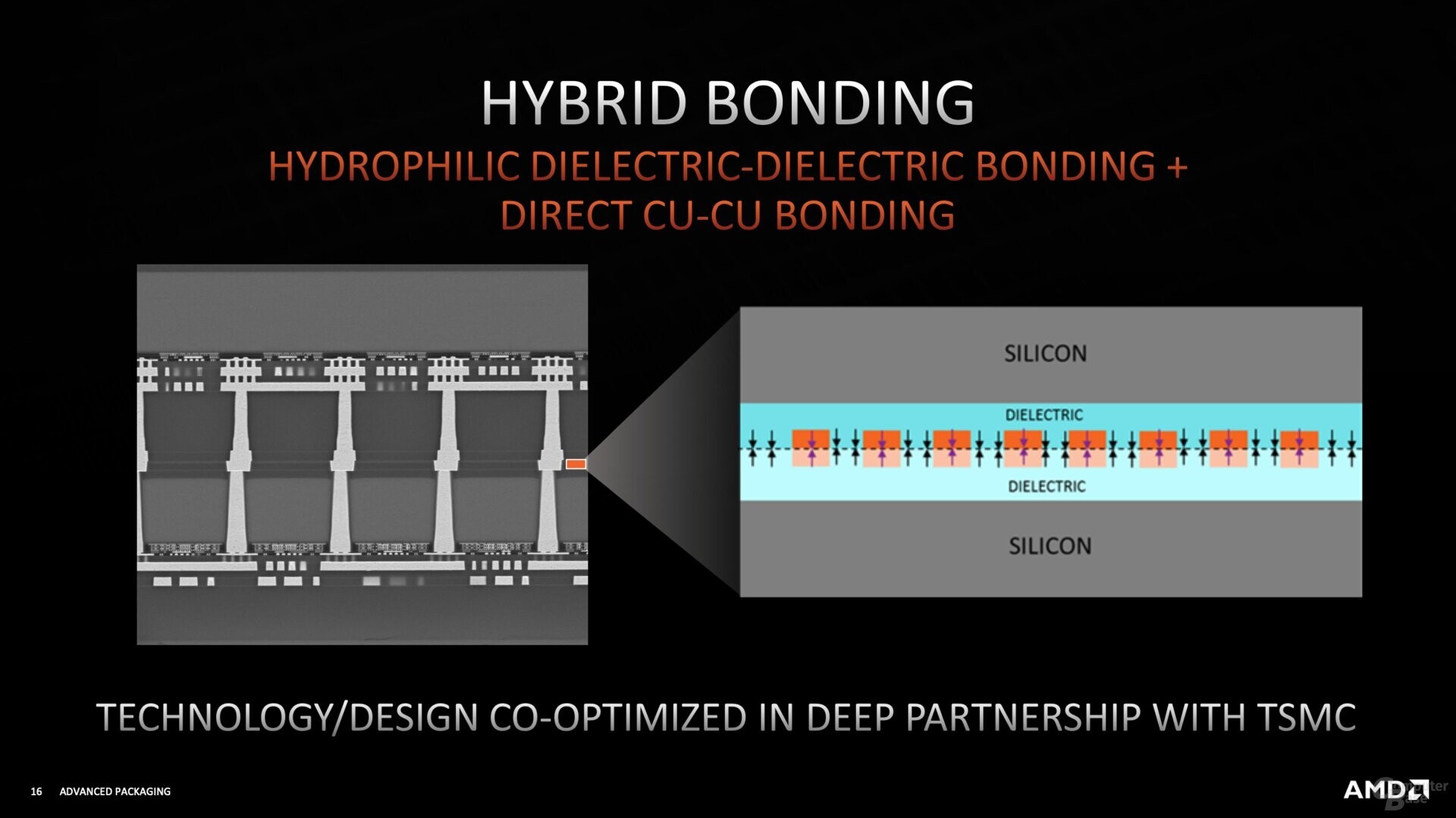

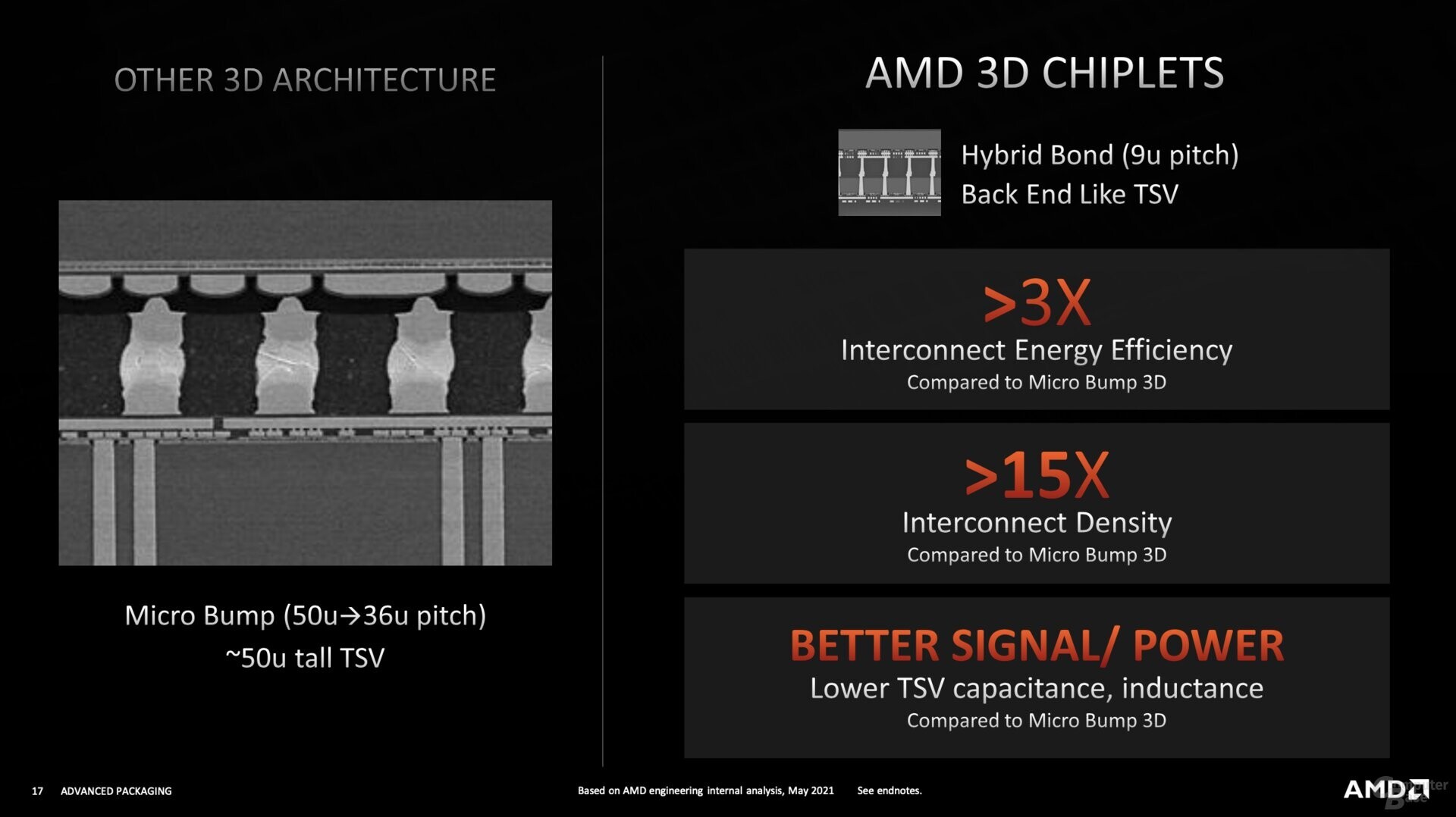

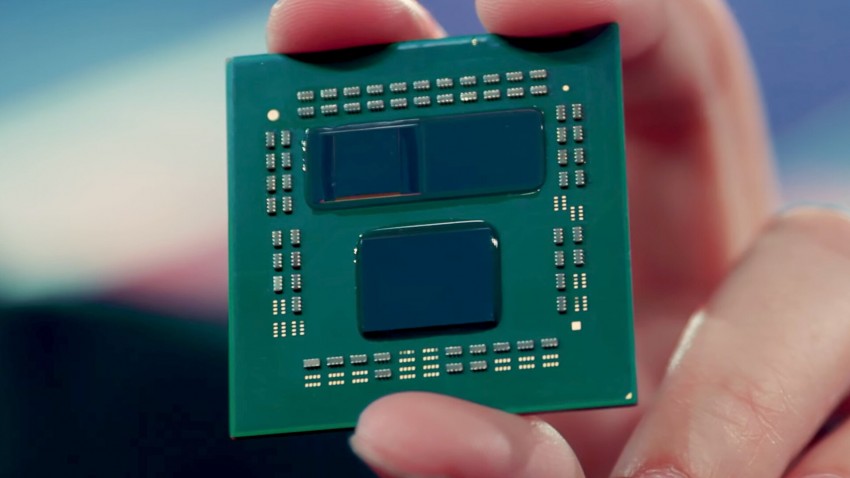

وهي عبارة عن قوالب SRAM بسعة 64 ميجابايت مكدسة فوق وحدات CCD "Zen 3". والتي ستعمل كامتداد لذاكرة التخزين المؤقت ذات الـ 32 ميجابايت من فئة L3 الموجودة حالياً. كما وقد أشارت الشركة أن النتوءات الصغيرة التي تربط ذاكرة التخزين المؤقت العمودية ثلاثية الأبعاد مع وحدات الـ CCD تأتي بحجم 9 ميكرون، مقارنة بـ 10 ميكرون في منتجات المنافس Intel Foveros.

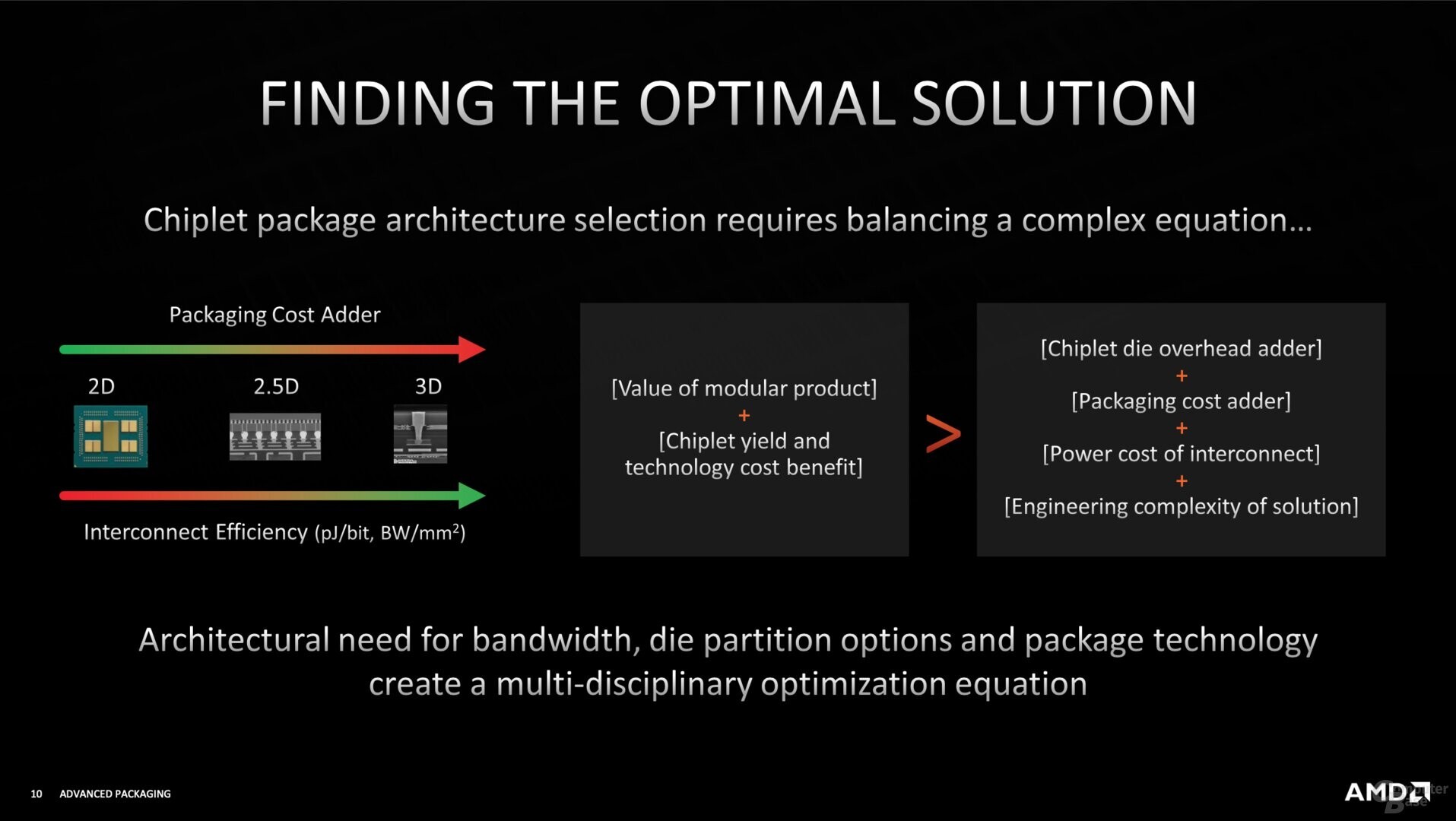

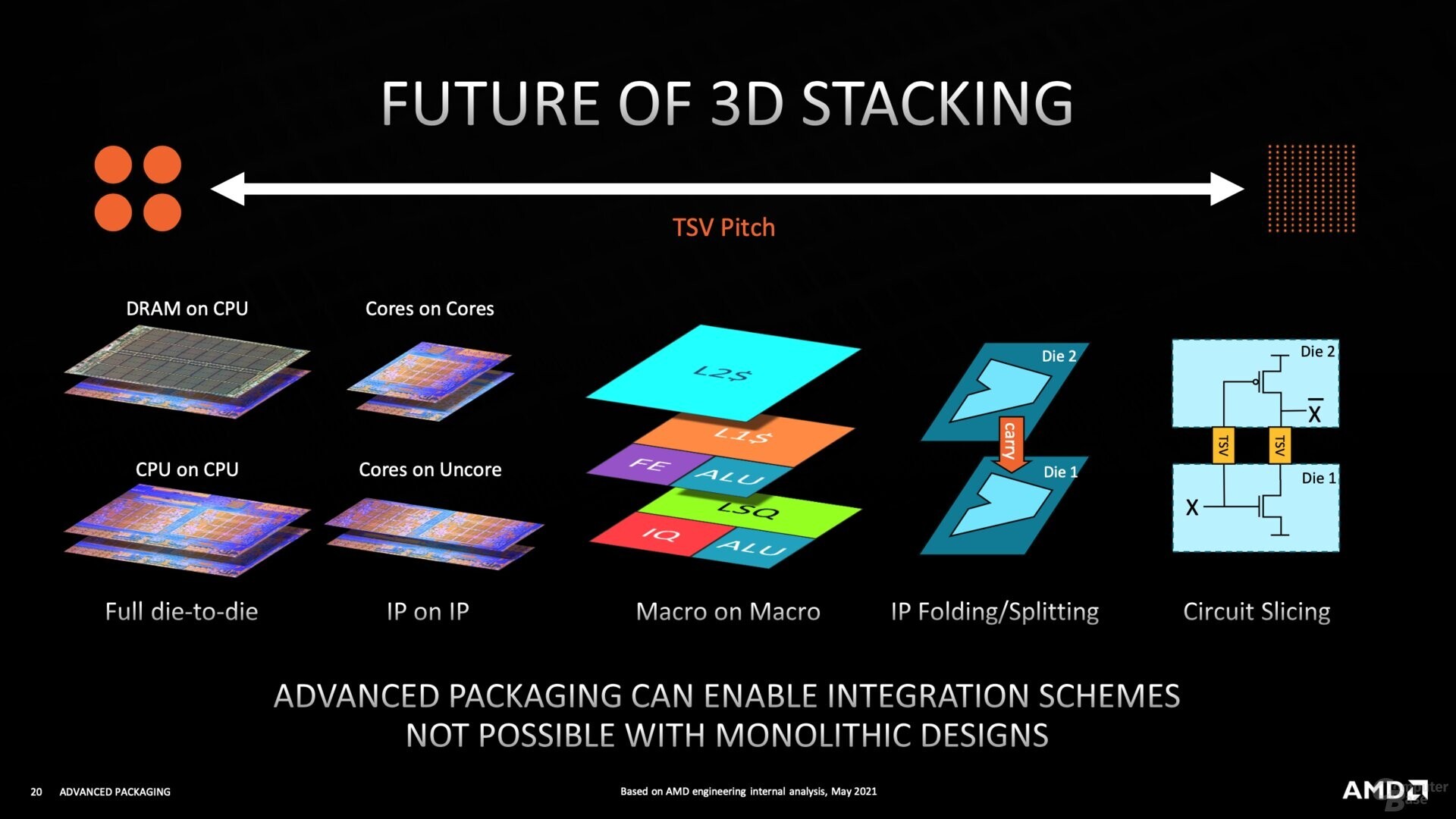

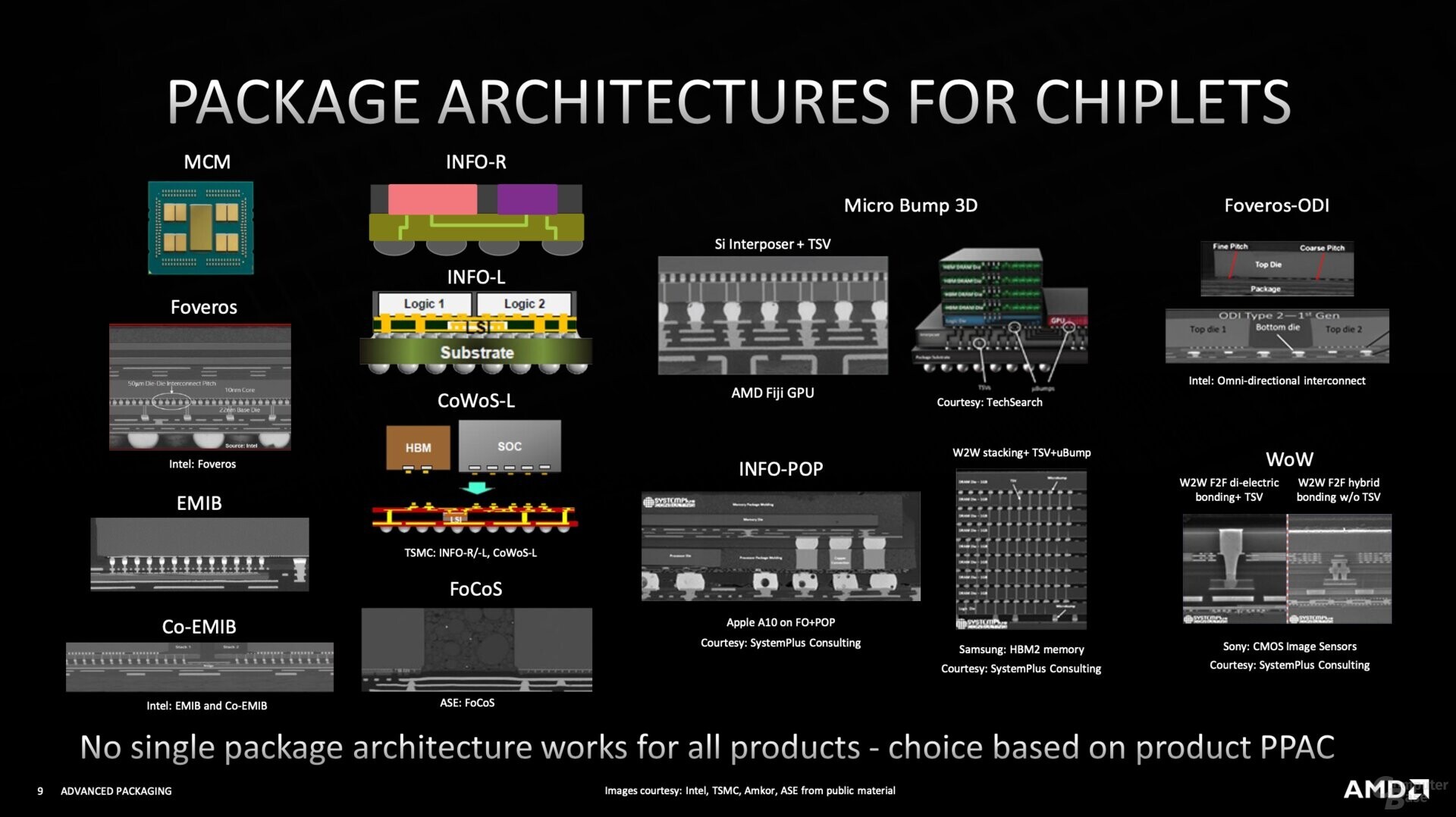

هذا وتؤمن AMD بأنه لا توجد تقنية تغليف واحدة تعمل مع جميع المنتجات، وأن الأمر يعتمد كليًا على ما تحاول تكديسه. كما وتحدثت الشركة عن مستقبل نظام التكديس بالقوالب المتراصة فوق بعضها die-on-die. فلأكثر من عقد من الزمان، كان تكديس الحزمة على الحزمة (package-on-package) ممكنًا (كما في حالة الهواتف الذكية). فحاليًا ، من الممكن وضع الذاكرة على الوحدات المنطقية في حزمة واحدة memory-on-logic، أو بين القالب المنطقي وشريحة SRAM للحصول على ذاكرة تخزين مؤقت إضافية؛ أو وضع القالب المنطقي لذاكرة الوصول العشوائي (DRAM) لذاكرة الوصول العشوائي المدمجة مع الحزمة؛ أو حتى وضع الوحدات المنطقة مع وحدات فلاش NAND لأجهزة الخوادم شديدة الكثافة.

لذا فالإحتمال المستقبلية غير محدودة. حيث تقول الشركة "تخيل تكديس وحدات CCDs مباشرة فوق وحدات cIOD أو شرائح sIOD لتقليل أثر وحجم اللوحة المطبوعة PCB للحزمة؛ أو استخدام التكديس ثُلاثية الأبعاد لتكديس الأنوية أعلى بعضها البعض، وهو ما يعني زيادة في عدد الأنوية وحجم أقل للشريحة ككل.

أما المستوى الذي يتخطى ذلك، فهو تقسيم النواة نفسها إلى أجزاء، وتكديسها بعد ذلك. حيث يُمكن أن يشهد هذا وضع المكونات الأكثر سخونة -مثل مرحلة التنفيذ مع خطوط أنابيب FP و INT الخاصة بها- على قالب مختلف عن الوحدات الأمامية ووحدات تخزين التحميل الأكثر برودة نسبيًا؛ بينما تظل الذواكر المخبئية من المستوى الأول والثاني L1 و L2 الأبرد نسبيًا متموضعة في الشرائح الأدنى.

لذا فالمستقبل البعيد لتقنيات التكديس لشرائح السيليكون يرى الدوائر الفردية منتشرة عبر قوالب مكدسة متعددة، مع التوصيل بينهم عن طريق وحدات TSVs (through-silicon vias) التي تربطها. كما أنه مع كل دفعة بين الأجيال، تتوقع AMD أن تزداد أحجام (وكثافة) وحدات الـ TSV.