بعض التفاصيل حول معمارية AMD Steamroller, الجيل الثالث من نواة Bulldozer

قام المسؤول الفني الخاص بشركة AMD بالإعلان عن أول التفاصيل الخاصة بنواة Steamroller الجديدة في مؤتمر Hot Chips السنوي.

قام المسؤول الفني الخاص بشركة AMD بالإعلان عن أول التفاصيل الخاصة بنواة Steamroller الجديدة في مؤتمر Hot Chips السنوي.

Steamroller هو الجيل الثالث من معمارية AMD Bulldozer, الذي وصل إلى السوق في نهاية عام 2011, الشركة ستبقى تعمل على هذه المعمارية "Bulldozer" للقيام بتصميم آخر بعد Steamroller على الأقل, فشركة AMD تخطط حالياً لعمل تحديث سنوي للمعمارية, فعلى سبيل المثال بالنسبة لعام 2012, نجد أن الشركة ستقوم بإطلاق تحديث Piledriver للمعمارية, و هى منصة Bulldozer محسنة, و التي تم بناء معالجات Trinity APU عليها, خلال نهاية هذا العام, سنجد أيضاً معالجات الفئة العليا بدون معالجات رسومية, و ستكون هذه المعالجات القوية قائمة على تحديث Piledriver.

تحديث Piledriver سينتج عنه معالجات تستهلك طاقة أقل من المعالجات الموجودة حالياً, المؤسف هو أن أداء المعالجات لن يزداد عن الحالية, فالميزة الوحيدة للتحديث الجديد, هو أن المعالجات الجديدة ستأتي بإستهلاك طاقة أقل بنسبة تتراوح من 10% إلى 20%.

تحديث Steamroller على الجانب الآخر, يستفيد من أساسيات Bulldozer و Piledriver, و يضيف إليهم المزيد من التحسينات التي سينتج عنها زيادة في الأداء, بجانب هذا, سيتم تصنيع تحديث Steamroller على دقة التصنيع 28nm, و هى لا تعتبر تغيير كبير عن دقة التصنيع المستخدمة حالياً, و هى 32nm.

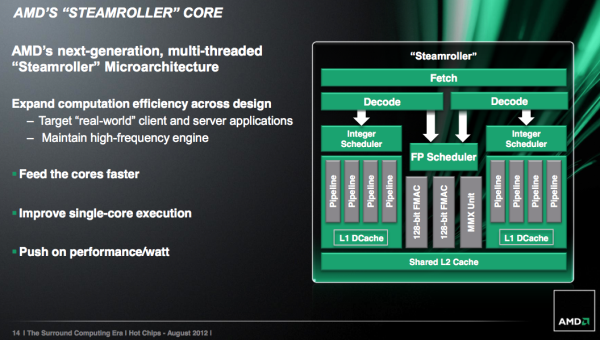

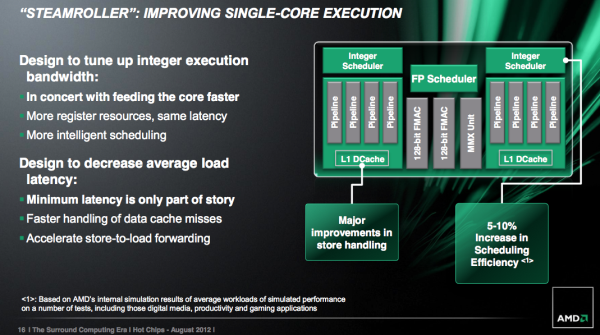

التحسينات التنفيذية على Steamroller:

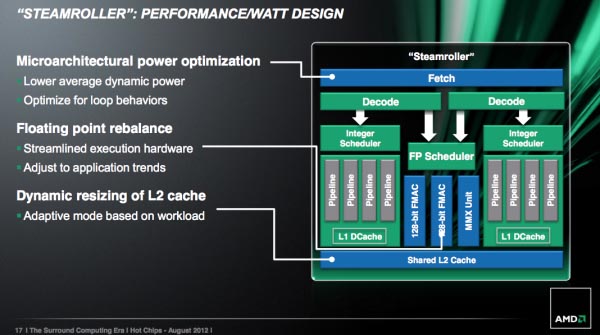

قامت شركة AMD بتبسيط وحدات الفاصلة العائمة "Floating Point" الكبيرة في كل وحدة Steamroller, لم يتم أي تغيير في القدرات التنفيذية الخاصة بال FPU "Floating Point Unit", و لكن تم تقليل المساحة العامة فيها, وحدة MMX في تحديث Steamroller تشارك بعض الهاردوير مع أنابيب 128-Bit FMAC, لم تقم شركة AMD بالتكلم بتفصيل حول هذا الأمر, و لكنها قالت فقط, أن الهاردوير المشتركة تتم فقط لعمليات MMX/FMA/FP المتبادلة.

تقليل موارد الأنابيب "الممرات" من المفترض أن يقدم نفس النتيجة بإستخدام طاقة و مساحة أقل, و هذه يعتبر طريقة إستخدام أفضل لل FPU من التي تم إستخدامها مع Bulldozer و Piledriver.

لا يوجد هناك تغيير في وحدات التنفيذ الصحيحة نفسها, و لكن هناك تحسينات آخرى تزيد من الأداء.

النقاط العائمة "الفاصلة العائمة" و وحدات التنفيذ الصحيحة أكبر في تحديث Steamroller, و لكن, شركة AMD لم تعلن عن مقدار نموهم, عمليات الضغط أيضاً تم ضغطها بحيث أنها تستهلك مدخل واحد في السجل الملفي, و هذا يساعد على زيادة فعالية كل RF.

تمت أيضاً زيادة أحجام نوافذ الجدولة, مما سينتج عنه إستغلال أكبر للموارد التنفيذية.

تحسينات Cache على Steamroller

تعليمات L1 Cache المشتركة تمت زيادة حجمها مع تحديث Steamroller, و لم تعلن شركة AMD عن مدى الزيادة في الحجم حتى الآن, معمارية Bulldozer تأتي بتعليمات 64KB L1 Cache ذات إتجاهين, و كل نواة تستخدم واحدة من هذين الإتجاهين, هذه الطريقة جعلت معمارية Bulldozer تستخدم Cache أقل لكل نواة عند مقارنتها بالمعماريات السابقة الآخرى, و لذلك عملية الزيادة هنا تعتبر شيء منطقي جداً, فشركة AMD تقول أن حجم L1 الزائد يستطيع تجنب أخطاء i-caches بمقدار 30%, لم تعلن شركة AMD عن أي تفاصيل بخصوص حجم L1 d-cache.

Steamroller ستأتي بصف Micro-OP" Micro Operation", بما أن تعليمات x86 يتم فك شفرتها إلى Micro-Ops, يتم تخزين العمليات التي تم فك شفرتها و العنوان الخاص بها في صف واحد, و هو صف ال Micro-OP, التصميم الجديد هذا شبيهة بتصميم uop Cache الخاص بمعالجات Sandy Bridge, و لكن الفرق هنا أن حجم التصميم الخاص بشركة AMD أقل حجماً, فشركة AMD لم تهتم بأقصى عدد لل Micro-Ops التي يمكن وضعها في صف واحد, كإهتمامها بأفضل كمية قادرة على تقديم أفضل أداء.

بجانب هذا, تم أيضاً تحسين واجهة L1 To L2.

بجانب هذا, يأتي Steamroller ب L2 Cache قابل لتغيير حجمه بشكل حيوي جداً, فعلى أساس الضغط و سرعة ال Cache, يمكن لمعالجات Steamroller إعادة تحجيم L2 Cache الخاص بها (تقليل حجمها عند عدم الإحتياج إلى طاقة المعالج الكاملة( بمقدار ال 1/4 كل مرة, و تعتقد شركة AMD أن هذا مفيد جداً للتطبيقات مثل فك شفرات الفيديو, و الذي يعمل فيه المعالج بكامل قوته لفترات قليلة جداً لتشغيل مهام بسيطة لا تحتاج إلى حجم L2 Cache كبير, L2 تستحوذ على مساحة كبيرة من نواة AMD, لذلك, عند إلغاء نصف L2 Cache أو أكثر, يمكن زيادة العمر الإفتراضي للبطارية بشكل ملحوظ "إذا كان الشخص يعمل على جهاز محمول".

تحديث Steamroller يبدو أنه يعتبر تحسين ثوري لمعمارية Bulldozer و Piledriver, ففي حين أن تحديث Piledriver يركز فقط على إستهلاك الطاقة, يركز تحديث Steamroller على الأداء بشكل أكبر, تحديث Steamroller سيأتي إلى الأسواق في عام 2013, و سيكون قائماً على دقة التصنيع 28nm, و لكن هل تعتقد أنه سيستطيع التنافس مع معالجات Intel Haswell؟