AMD تضاف الـL3 Cache لكل CCX في معمارية Zen 2 (Rome)

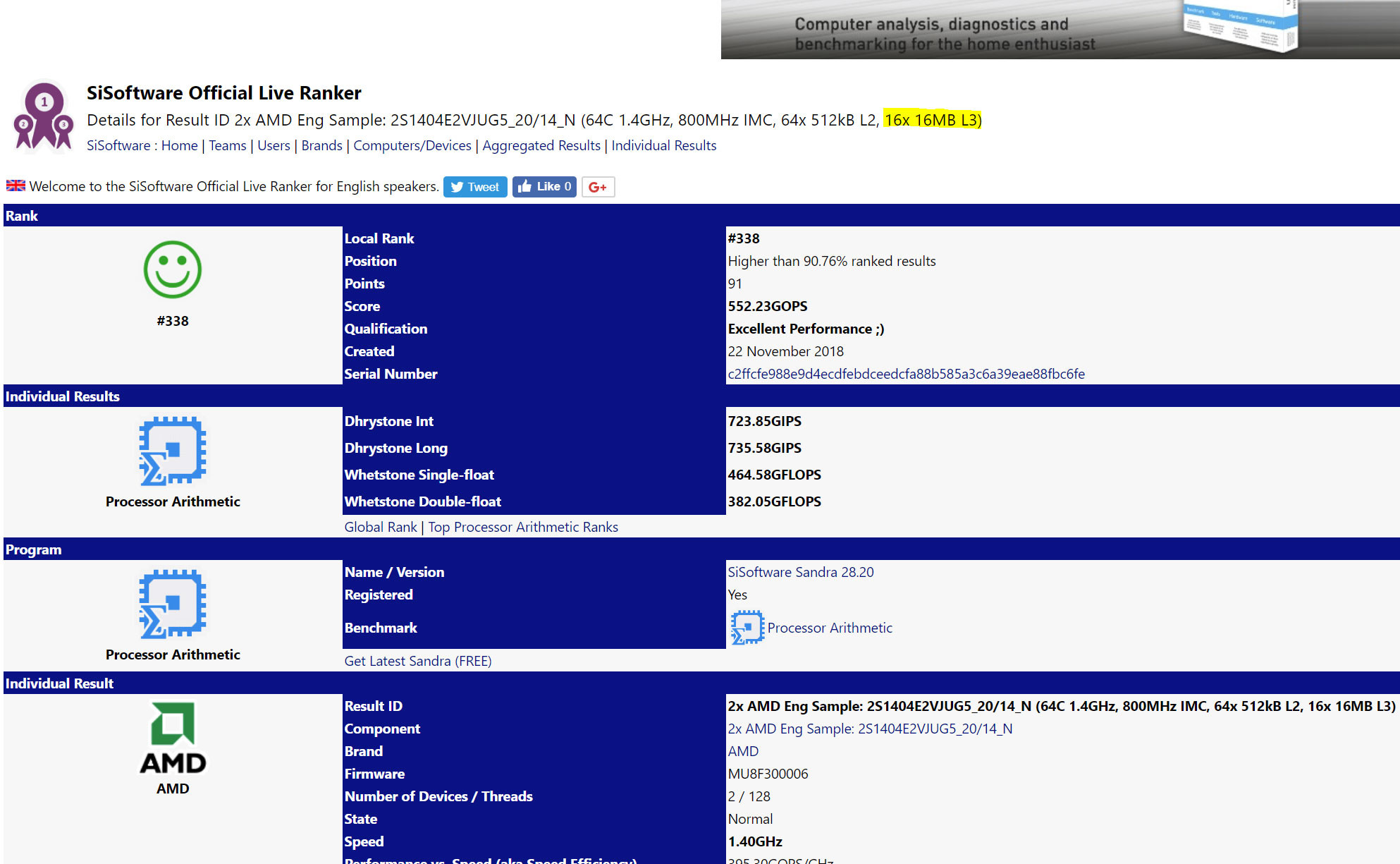

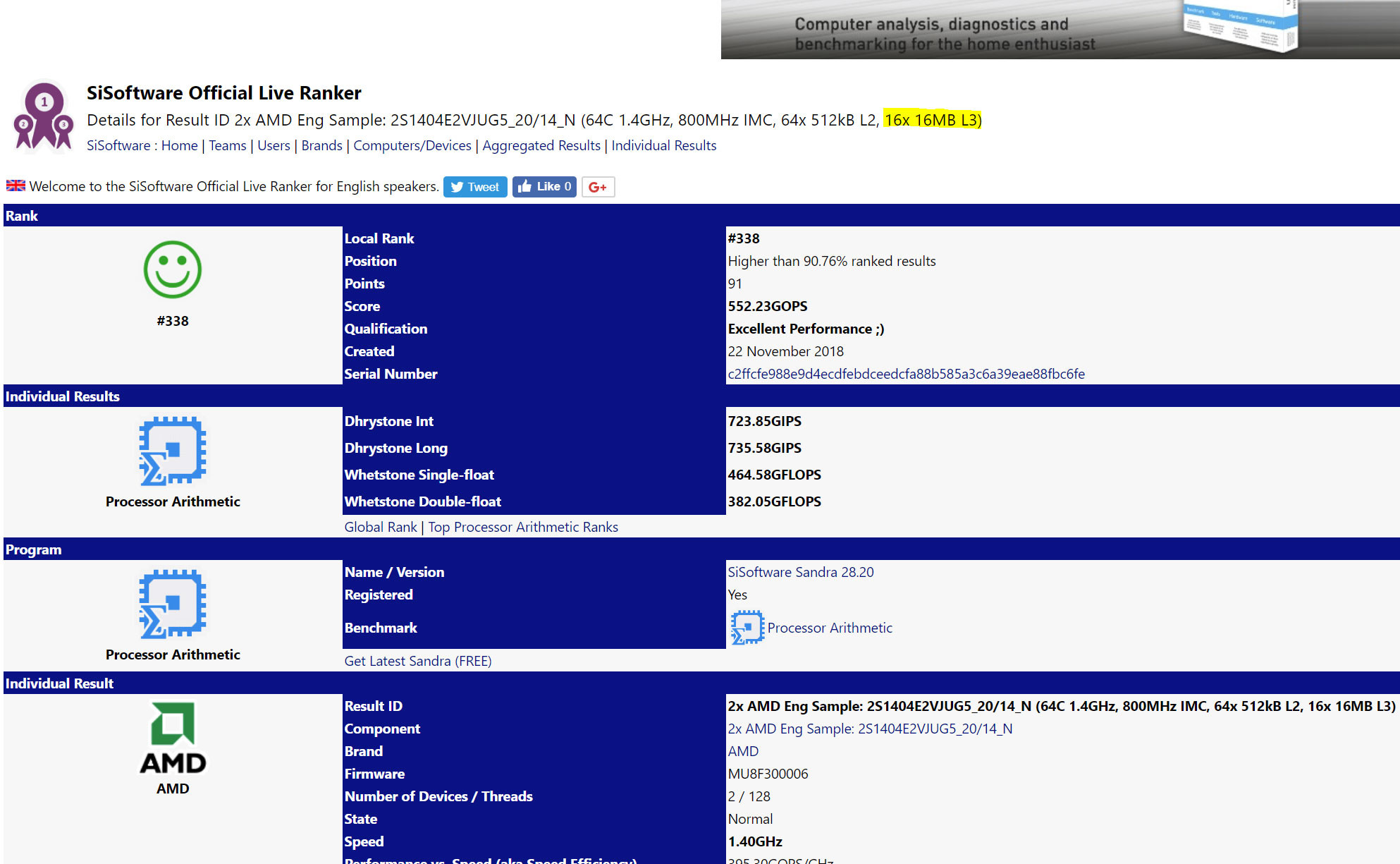

تم إجراء تجارب من خلال SiSoft SANDRA على الـ2P AMD (Rome) EPYC والذي يتكوّن كل معالج من 64 نواة وما يصل إلى ثمان شرائح Zen 2 بدقة تصنيع 7 نانومتر والتي يتم تشغيلها من خلال Controller Die بدقة 14 نانومتر للإدخال والإخراج I/O وهو ما يعمل على إدارة وضبط توصيل الـPCIe، ومن خلال التجارب تم التعرف معمارية وهرمية الـCache في المعالجات أيضًا، حيث سيصل الـCache إلى 512 كيلوبايت لكل نواة.

سيأتي المعالج بكاش L3 على النحو 16x16 MB L3 في حال أن الكاش في معالج Ryzen 7 2700X كان يقرأ على النحو 2x8 MB L3 والأمر هنا قد تغير كما يظهر.

كل معالج من المعالجات سيأتي بـ64 نواة كما أسلفنا الذكر، والحديث هنا حول SANDRA ومعالجات Rome، حيث أن هذه التجربة أثبتت أن المعالجات تأتي بـ64 نواة أي أن كل ثمان نواة سيقدمون ذاكرتين 16 ميجابايت L3 Cache والثمان أنوية مقسمين إلى إثنين CCX من حيث الوحدات وكل منهم يحصل على ذاكرة 16 ميجابايت، وكما نعلم جميعًا، مضاعفة الـCache لكل وحدة CCX سيساعد المعالج على نقل البيانات بين من وإلى الـI/O Die بسرعة وسهولة.

ما رأيك في الأمر؟ شاركنا تعليقك