شركة AMD تتبنّى تقنية التكديس ثلاثية الأبعاد SoIC الخاصة بشركة TSMC

شركة AMD سوف تتبنّى تقنية التكديس ثلاثية الأبعاد من TSMC لتواجه تقنية Foveros الخاصة بانتل مع الجيل القادم من منتجات HPC الخاصة بها.

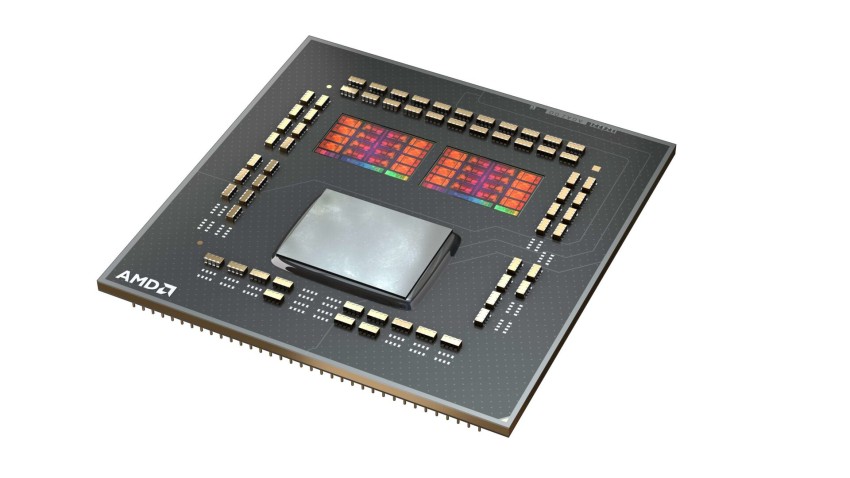

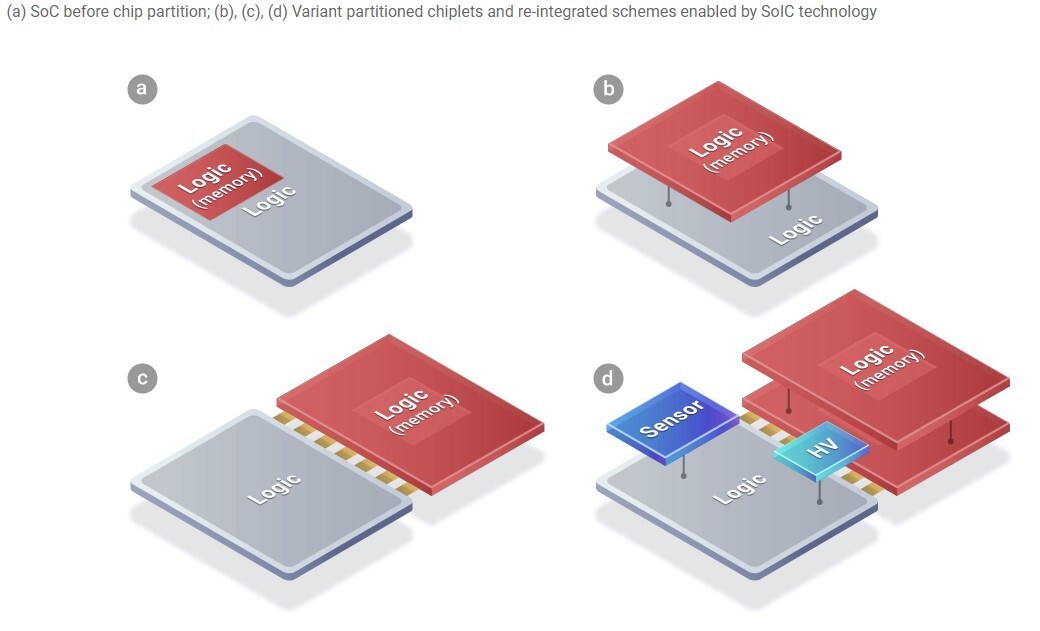

وفقًا لتقرير جديد صادر من DigiTimes، ستطلق شركة AMD تقنية TSMC الطموحة System-on-Integrated-Chips (SoIC) مع رقائق HPC القادمة الخاصة بها. وتُعتبر هذه خطوة كبيرة نحو المنافسة مع تقنية تكديس الرقائق ثلاثية الأبعاد من Intel والمعروفة باسم Foveros، حيث ستُمكّن تقنية تكديس SoIC شركة AMD من تكديس وحدات المنطق والذاكرة، وعناصر الإدخال/الإخراج كشرائح منفصلة داخل حزمة واحدة.

وتشير المقالة إلى شريحة "HPC" من الجيل التالي، على الرغم من أنها لم تتعمق في ما يمكن أن يكون عليه الجيل التالي. ومنطقيًا، قد ترغب AMD في دمج خطوط منتجات EPYC و MI في حزمة واحدة يمكن استخدامها في أنظمة الحواسيب عالية الأداء HPC الخاصة بها. سيجمع مثل هذا المنتج بين المعالجة التسلسلية من سلسلة Zen-series x86-64 ، والمعالجة العددية لسلسلة CDNA، وخبراتها في مجال الذاكرة، والاستفادة من تقنيات الذاكرة المخبأة victim-caches، وذاكرة النطاق الترددي العالي (HBM) ؛ مع الجيل التالي من واجهات I / O.

لم يذكر التقرير أياً من المعلومات حول الوقت الذي قد نرى فيه هذه التقنية.