TSMC تطلق شارة البداية لعملية تطوير عقدة تصنيع 2nm !!

طبقاً لتقرير DigiTimes

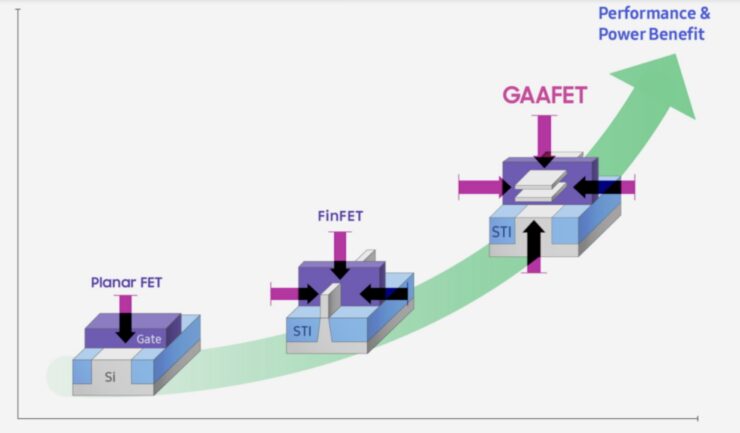

بعد الانتهاء من تقنية 5 نانومتر ، الذي يُتوقع أن تزود كثافة الترانزستور من 84-87٪ مقارنة بعقدة 7 نانومتر الحالية (طبقاً لبعض التصريحات والأخبار)، فإن التركيز كله سوف يذهب الى عملية 3 نانومتر ، حيث تتوقع TSMC أن تصل العقدة إلى مرحلة الإنتاج الكمّي الضخم بحلول عام 2022 . ومن المثير للاهتمام أن TSMC لا تزال تخطط لاستخدام تقنية FinFET من أجل عقدة التصنيع 3 نانومتر ، ولكن من خلال تقنية GAAFET (ترانزستورات تأثير المجال الشامل) .

بعد الانتهاء من تقنية 5 نانومتر ، الذي يُتوقع أن تزود كثافة الترانزستور من 84-87٪ مقارنة بعقدة 7 نانومتر الحالية (طبقاً لبعض التصريحات والأخبار)، فإن التركيز كله سوف يذهب الى عملية 3 نانومتر ، حيث تتوقع TSMC أن تصل العقدة إلى مرحلة الإنتاج الكمّي الضخم بحلول عام 2022 . ومن المثير للاهتمام أن TSMC لا تزال تخطط لاستخدام تقنية FinFET من أجل عقدة التصنيع 3 نانومتر ، ولكن من خلال تقنية GAAFET (ترانزستورات تأثير المجال الشامل) .