معالجات AMD EPYC Zen 4 حتى 128 نواة وبدقة 5nm..هل اصبح الحلم حقيقة؟

في عالم المعالجات المركزية هناك امور يمكن الوصول لها وهناك امور نحلم بأن تصبح حقيقة, قبل وصول معالجات Ryzen كنا نحلم بالوصول لمعالجات بـ 16 نواة أو 32 نواة أو حتى 64 نواة هو أمر صعب تحقيقه خلال السنوات القادمة, ولكن المفاجئ للجميع أن ذلك أصبح حقيقة على أرض الواقع.

الحلم الأخر الذي كان يعتبر بعيد المنال في هذه الفترة وهو الوصول لمعالجات بـ 128 نواة...اليوم هذا الأمر سيصبح حقيقة وأمراً واقعاً! كيف ومتى ولماذا نحن بحاجة إلى هذا الكم من الأنوية؟ ضمن هذا المقال سوف نخوض في التفاصيل المهمة التي تم الكشف عنها ضمن مؤتمر AMD Data Center.

معمارية Zen 4 بتصميم بنية انوية مختلفة؟

كنا نعلم منذ فترة أن عمليات التطوير والأبحاث بخصوص معمارية Zen 4 كانت قد بدأت منذ عام 2018, وفي عام 2019 كانت قد بدأت عمليات التصميم الخاصة بها فعلياً..اليوم نحن على موعد لرؤيتها مستخدمة مع المعالجات المركزية من مختلف الفئات بداية مع معالجات الخوادم EPYC لتدفع بمستوى الاداء نحو مراحل جديدة مع الأخذ بعين الاعتبار زيادة عدد الانوية نحو أرقام لم يسبق لنا أن رأيناها في تاريخ صناعة CPU.

خارطة الطريق الخاصة بمعالجات الخوادم EPYC كانت قد بدأت من عام 2017 مع معالجات NAPLES من معمارية Zen بدقة تصنيع 14nm ثم دخلنا نحو معالجات ROME من معمارية Zen 2 بدقة تصنيع 7nm وبعد ذلك نحو معالجات MILAN من معمارية Zen 3 بنفس دقة التصنيع 7nm, لنصل اليوم نحو دقة تصنيع 5nm "القادمة من مسابك TSMC" التي ستكون مستخدمة مع معمارية Zen 4.

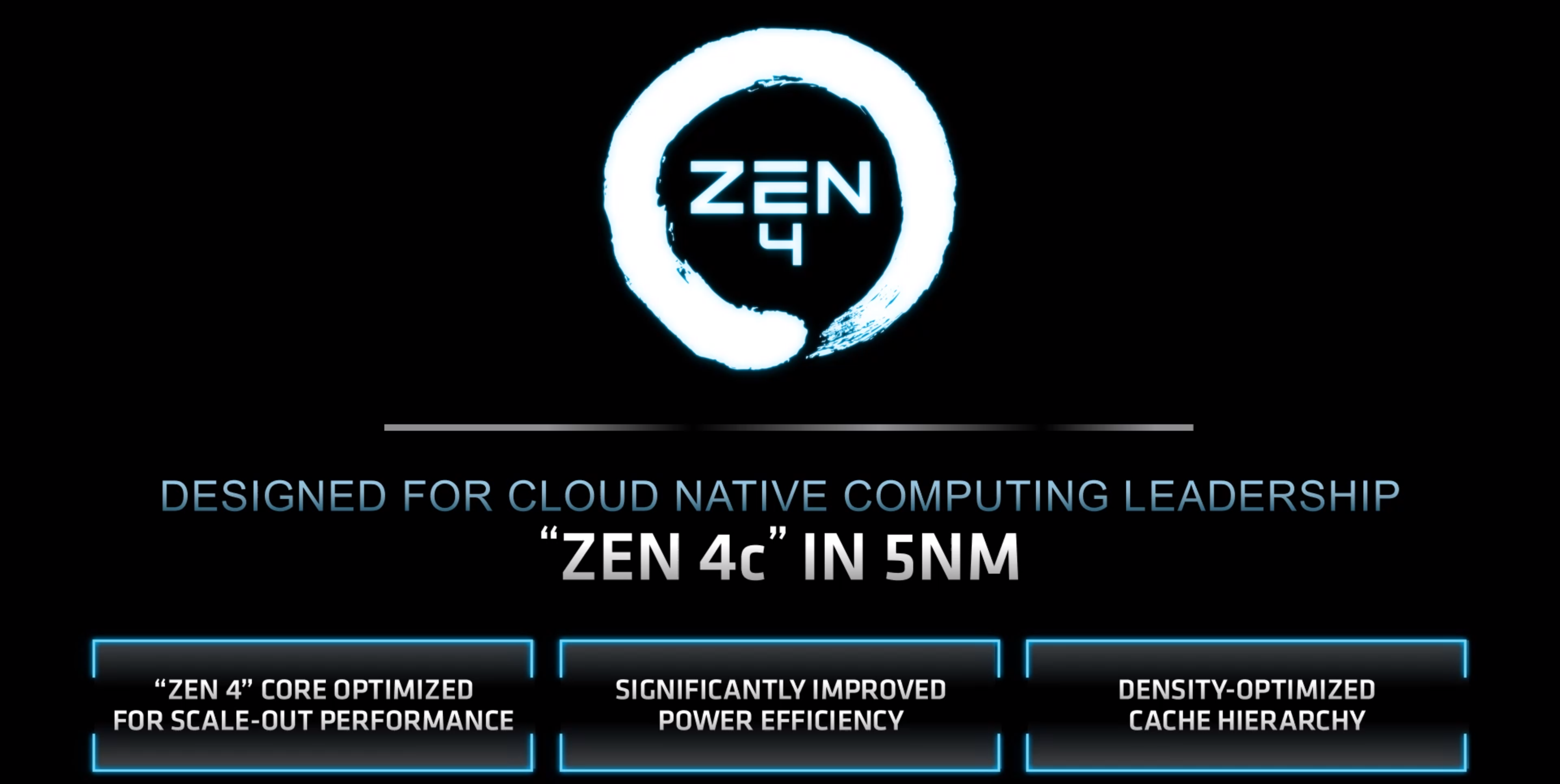

هذه المعمارية الجديدة التي ستصل أولاً نحو معالجات الخوادم EPYC من الجيل الرابع ستكون منشقة إلى قسمين من ناحية بنية النواة التي تعتمد عليها, فالتصميم التقليدي لها سيكون مستخدم مع معالجات EPYC GENOA بينما التصميم المحسن والخاص للفئة السحابية من الخوادم سيكون مستخدم مع معالجات EPYC BERGAMO لتحمل إسم Zen 4c.

من الواضح أن هناك هدف اساسي من AMD باستغلال كل الفرص المتواجدة لديها لتوسيع تواجدها في سوق معالجات الخوادم والسوق المهني التي ما زالت تسيطر عليه Intel بنسبة كبيرة, نعم النسبة تتقلص في كل عام لتهذب لصالح AMD ولكن ما زال الطريق طويل للحصول على حصة 50%.

الجيل الرابع من معالجات EPYC ستكون متوفرة ضمن فئتين:

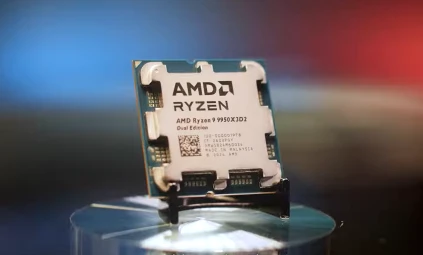

معالجات GENOA

هذه المعالجات ستستند على معمارية Zen 4 الجديدة مع تصميم أنوية قياسية مخصصة للتعامل مع جميع انواع التطبيقات إن صح التعبير, نعم سنحصل على تحسينات مختلفة على صعيد هذه المعمارية بلا شك مثل تحسينات IPC وهي تعني عدد التعليمات أو الاوامر التي أصبح المعالج قادر على معالجتها خلال النبضة الواحدة للتردد بجانب تحسين النواة نفسها ورفع التردد وزيادة عدد الانوية. ما نعرفه الان أن عدد الانوية مع هذا النوع من المعالجات سيصل حتى 96 نواة مستندة على انوية معمارية Zen 4 الجديدة.

هذه المعالجات ستعتمد على سوكيت جديد وستدعم الجيل الجديد من ذاكرة DDR5 وواجهة PCIe 5.0 بجانب CXL 1.1 و RAS ومجموعة أمان AMD الموسعه وسترى النور في عام 2022.

معالجات BERGAMO

اما هذه المعالجات فهي تأتي بتصميم أنوية Zen 4c chiplet ذات بنية مختلفة متناسبة مع حاجة المراكز السحابية التي تتطلب عدد أكبر من الأنوية, وفعلياً هذا ما تقدمه بنية الانوية الجديدة التي مبدئياً تبدو أصغر حجماً ولكن أكثر عدداً لتصل إلى 128 نواة مستندة على أنوية معمارية Zen 4c ويرمز حرف c إلى " cloud optimized". بهذه البنية المختلفة نحن نتحدث عن تحقيق قفزة إضافية في الأداء ستكون لصالح الحلول السحابية ضمن مراكز البيانات.

نعم كلاهما سيعتمدان تقريباً على نفس ألية تنفيذ المهام والوظائف ولكن الاختلاف الأهم هو حصول هذه الأنوية على كثافة أكبر من ناحية تعداد الانوية "التي يقال أنها أصبحت أصغر حجماً" لتتناسب مع نظرية الاداء مقابل الطاقة. ماذا يعني ذلك؟ يعني أن هذه الأنوية سوف تركز على تحقيق الاداء الأفضل "ربما نشهد زيادة في IPC مقارنة بأنوية Zen 4 القياسية" مع تعداد أنوية أكبر على حساب استهلاك الطاقة لتتجاوز تقريباً ما نراه مع معالجات الخوادم التي تصل عادة حتى 280 واط.

ماذا عن الذاكرة المخبأة؟ حتماً سنرى حجم أكبر من الذاكرة المخبأة ذات المستوى الثالث التي ستساعد على تحسين عمل الأنوية بشكل عام, حتى اللحظة لا نعرف إن كان هناك اعتماد على ذاكرة 3D V-Cache التي أثبتت قدرتها على تحسين الأداء ضمن نفس بنية تصميم الرقاقة فقط بمضاعفة الذاكرة من خلال هذه التقنية لتسمح بزيادة الأداء بنسبة جيدة دون أي متطلبات على صعيد استهلاك الطاقة, وبما أنها بتصميم chiplet فهذا يعني أن كل مجموعة سيكون لها مخزونها الخاص من الذاكرة المخبأة.

للأسف المعلومات حول قالب IO بجانب واجهة المعالج الداخلية ما زالت غير معروفة وننتظر المزيد من التفاصيل في الأشهر القادمة لكي نفهم أكثر بنية هذه الانوية المختلفة ضمن معمارية Zen 4 إلا أن ما نستطيع تأكيده بناء على ما صرحت به ليزا هذه الأنوية الجديدة Zen 4c المصنوعة بدقة 5nm HPC من مسابك TSMC سوف توفر كثافة أكثر بمرتين وكفاءة طاقة أفضل بمرتين مع أداء أعلى بـ 1.25 مرة مقارنة بتصميم رقاقة السيليكون على دقة 7nm من TSMC. هذه التفاصيل تعطينا نظرة على مدى الفائدة التي ستحصل عليها تلك الأنوية المختلفة بفضل دقة 5nm مقارنة بـ 7nm.

هذه المعالجات ستعتمد أيضاً على سوكيت جديد "نفس سوكيت معالجات GENOA" وستدعم الجيل الجديد من ذاكرة DDR5 وواجهة PCIe 5.0 بجانب CXL 1.1 و RAS ومجموعة أمان AMD الموسعه وسترى النور في نهاية عام 2022 أو في بداية عام 2023.

معالجات Milan-X...بماذا ستختلف عن معالجات EPYC الحالية؟

معالجات EPYC Milan الحالية من الجيل الثالث المستندة على معمارية Zen 3 ما زلت قوية وقادرة على تقديم تجربة ممتازة في مختلف المجالات المهنية إلا أن رغبة AMD بتحسين تلك المعالجات جعلها تفكر بطرح معالجات Milan-X وهو تحديث محسن لبنية الرقاقة من ناحية الذاكرة المخبأة لتساعد على تحسين الأداء بشكل أكبر دون التأثير على معدل استهلاك الطاقة مبدئياً, فرغم أنها على نفس السوكيت الحالي وهو SP3 إلا أن الحديث حول الترددات أو معدل استهلاك الطاقة ما زال طي الكتمان.

الفكرة من وراء هذا التصميم هو إضافة حجم مضاعف من الذاكرة المخبأة لكل CCX, وهي نفس الفكرة التي رأيناها نوعاً مع إصدار خاص من معالج Ryzen 9 5900X المعتمد على هذه التقنية والتي حصلت على ذاكرة SRAM مخبأة بحجم 64MB وبدقة تصنيع 7nm المكدسة بشكل عامودي فوق قالب CCD ليكون الهدف مضاعفة الحجم الكلي للذاكرة المخبأة من المستوى الثالث والتي تستفيد منها انوية المعالج المركزي بشكل مباشر.

حجم الذاكرة المخبأة من المستوى الثالث مع معالجات EPYC Milan الحالية هو 256MB وذلك لأن هذه المعالجات تستند بتصميمها على ثمانية CCX بعدد أنوية يصل إلى 64 نواة, كل واحد منها متصلة بذاكرة مخبأة من المستوى الثالث بحجم 32MB أي ان المجموع الكلي هو 256MB والمصنوعة كذلك بدقة 7nm. المختلف مع معالجات EPYC Milan-X المحسنة هو اعتمادها على نفس بنية أنوية معالجات Milan التي تصل حتى 64 نواة موزعة على ثمانية انوية لكل CCX لكن بدلاً من وضع ذاكرة مخبأة من المستوى الثالث بحجم 32MB لكل CCX تم مضاعفة ذلك الحجم حتى 96MB.

سأشرح لكم الأمر بشكل أكثر دقة: ما قامت به AMD ليس إزالة حجم 32MB ووضع حجم 96MB من الذاكرة المخبأة ولكن ما قامت به هو إضافة ذاكرة مخبأة 3D V-Cache بحجم 64MB المصنوعة بشكل محسن وذات كثافة أعلى بفضل تقنية 7nm لتوضع بشكل مباشر فوق الذاكرة المخبأة الموجودة مسبقاً على الرقاقة بحجم 32MB, ليكون المجموع الكلي من الذاكرة المخبأة من المستوى الثالث لكل CCX هو 96MB..نحن نتحدث عن 768MB بدلاً من 256MB مع معالجات EPYC Milan مع الأخذ بعين اللاعتبار تحسين بنية قالب الرقاقة على النقل الحراري بشكل أفضل. إن كنت تتسائل لماذا الصورة تخبرنا بأن الحجم هو 804MB؟ بكل بساطة لأن هذا الرقم يعني الحجم الكلي للذاكرة المخبأة من كل المستويات: حجم 768MB من الذاكرة المخبأة من المستوى الثالث و حجم 32MB من الذاكرة المخبأة من المستوى الثاني و حجم 4MB من الذاكرة المخبأة من المستوى الأول = 804MB.

المؤكد الأن أن هذه المعالجات المحسنة سوف يتم البدء بإنتاجها في نهاية عام 2021 لتتوفر في الأسواق في الربع الأول من عام 2022 مع توقعات بأن تكون بأسعار مرتفعة مقارنة بالجيل الحالي عطفاً على زيادة الأداء التي حصلت عليها.