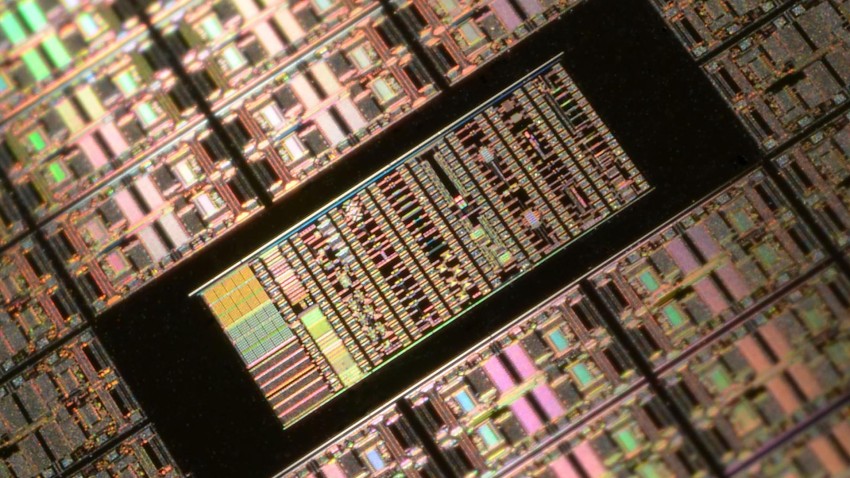

Intel تعمل على تقنية تصميم جديدة قد تزيد عدد الترانزستور مع دِقَّة 2nm

حتى اللحظة كل ما سوف تشاهده من تفاصيل عبارة عن أبحاث لبراءة اختراع قيد التسجيل من Intel لم يتم تنفيذها على أرض الواقع، إنما خطط مستقبلية قد تكون قابلة للتنفيذ خلال السنوات القادمة، وبنفس الوقت ربما تكون عبارة عن أبحاث ورقية لا أكثر أي لن ترى النور فعليًا.

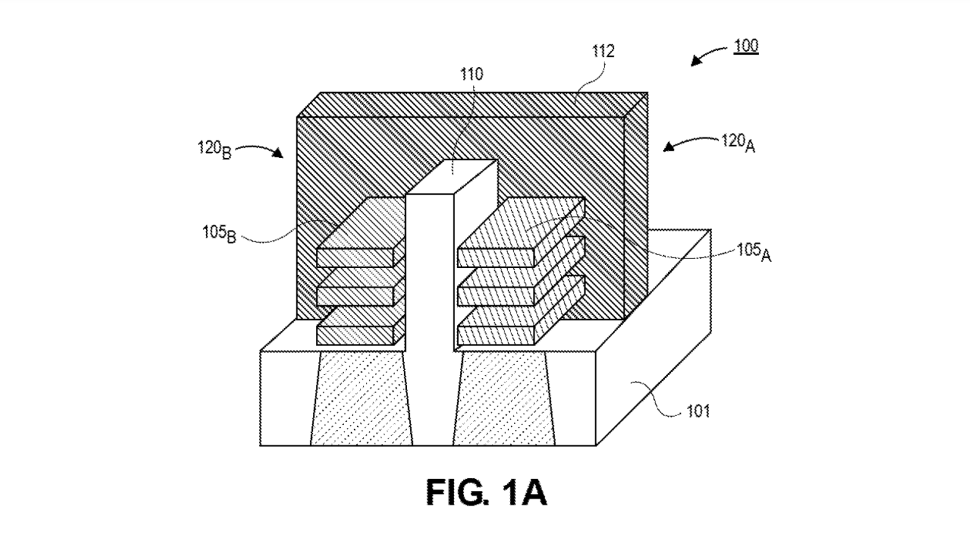

وفقًا للمعلومات المتاحة يبدو أن Intel تعمل في الوقت الحالي على تطوير تقنية تصميم ترانزستور جديدة لتستخدم مع دِقَّة تصنيع 2nm. التصميم الجديد الذي يُنعش من جديد الأمال نحو قانون مور يحمل إسم "Stacked Forksheet Transistors" وقد يدخلنا نحو معمارية CMOS ثلاثية الأبعاد مكدسة بشكل رأسي.

من خلال هذا التصميم سيسمح لنا بزيادة عدد الترانزستور مقارنة بتصاميم "Tri-Gate" المتطورة والأكثر تقدمًا في الوقت الحالي. مع ذلك هناك تعقيدات تقف في طريق هذا التصميم، لأن التكلفة المالية والمخاطر من فشل التصميم والتعقيدات الهندسية قد تكون أكبر من النتائج الإيجابية.

من التفاصيل المهمة التي حصلنا عليها أيضًا، هي الحديث حول الترانزستورات النانوية المقترنة برقائق من مادة الجرمانيوم الرفيعة لتعمل كجدار عازل للكهرباء الداخلية أي سيكون هناك جدار فاصل بين الطبقات، وهذا يعني وجود عازل بين P-Gate و N-Gate ضمن كل طبقة من طبقات الترانزستور المكدسة بشكل رأسي. ماذا يعني ذلك بشكل مُبسط؟ يعني إمكانية وضع المزيد من الطبقات ضمن مساحة أصغر لينعكس بشكل إيجابي على بنية التكديس الرأسية رُغم تعقيدات المساحة الصغيرة التي ستضم كل هذا الكم من الطبقات.

هل كشفت Intel عن التحسينات التي يمكن أن تطرأ على كثافة الترانزستور والأداء وكفاءة الطاقة؟ للأسف لا، فحتى اللحظة لانعرف شيء حول هذا الأمر، لكن ما قد يساعدنا على الوصول لتوقع يخص تلك المعطيات هو ما أعلنت عنه Imec ، وهي مجموعة من الباحثين كانت قد كشفت في عام 2019 عن تطوير أول نتائج محاكاة خلية قياسية لـ "Forksheet Devices". ووفقًا لنتائج محاكاة الخلية القياسية الأولى عند تطبيقها على دقة تصنيع 2nm، يمكن لهذه التقنية توفير تحسينات كبيرة في كثافة الترانزستور مقارنة ببنية Nanosheet التقليدية.

بالأرقام نحن نتحدث عن زيادة السرعة بنسبة 10% أو تحسين كفاءة الطاقة بنسبة 24% بسرعات ثابتة ، مع تقليل مساحة الخلية بنسبة تزيد عن 20%. بالإضافة إلى ذلك ، فإن مساحة ذاكرة الوصول العشوائي (SRAM) التي تُعتبر المغذي لذاكرة التخزين المخبأة لوحدة المعالجة المركزية وتستحوذ على مساحة كبيرة من قالب الرقاقة قد تنخفض بنسبة 30%!

إذاً نحن أمام فترة زمنية طويلة نوعًا ما حتى يتبين لنا إن كانت Intel ستغامر نحو هذا التصميم الجديد مع دقة 2nm خاصة بعد تأكيد عدة مصادر بأن Intel تقوم حالياً بطلب براءة اختراع لما وصلت له مع هذا التصميم مما يعني أن هناك عدة مزايا مهمة قد تستخدم في وقت ما.