دقة 5nm من TSMC ستقدم عدد ترانسستورات أكثر بنسبة 87% من الجيل الحالي!

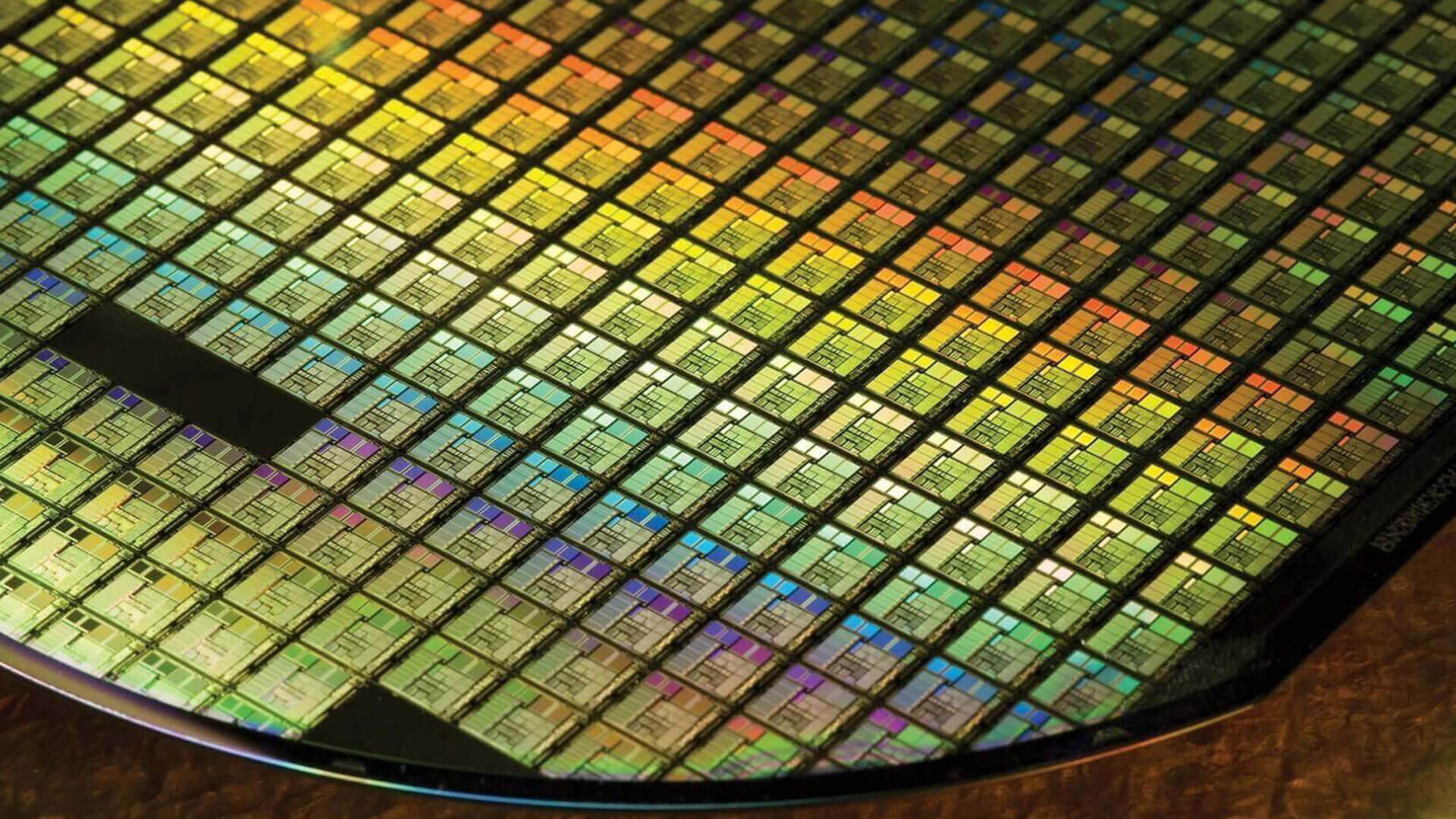

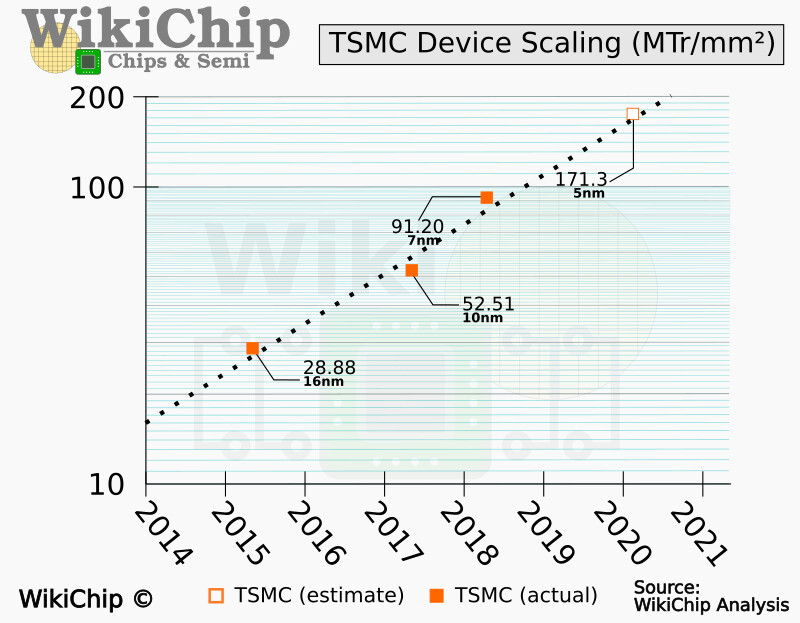

في الفترة الحالية يستعد الكثير من المتابعين والمحللين والشركات على حد سواء لإستقبال دقة تصنيع 5nm الخاصة بشركة TSMC ، والتي من المتوقع أن تقدم نقلة كبيرة أخرى في الأداء مقارنة بما تقدمه الدقة الحالية 7nm من الشركة . ومن هذا المنطلق يُقدّر تحليل WikiChip للجيل التالي من عقدة تصنيع السيليكون المنتظرة والمعروفة باسم N5P أو 5nm الخاصة بشركة TSMC زيادة هائلة بنسبة تصل حتى 84-87 ٪ في كثافة الترانزستور الموجودة على الشرائح مقارنة بأول عقدة تجارية مبنية على دقة تصنيع 7 نانومتر أو N7 (7nm DUV) .

ويقدر التقرير أن هناك زيادة بنسبة 87٪ في كثافة الترانزستور سوف تتواجد مع دقة التصنيع الجديدة ، على الرغم من أن الرقم الخاص بـ TSMC نفسها أقل قليلاً حيث يصل الى 84٪ في أفضل الحالات . و من المتوقع أن تبدأ العقدة TSMC N5P في الدخول الى مرحلة الإنتاج في وقت لاحق من هذا العام (في حال سارت الأمور على ما يرام ) . الجدير بالذكر أن المرحلة الأولى من دقة التصنيع TSMC N5 ، بدأت مرحلة الإنتاج في وقت سابق من هذا العام ، مع التخطيط لبدء عمليات الإنتاج الكمي على العقدة في شهر أبريل أو مايو القادمين (في حال لم يتم تأجيل أو إبطاء العملية عن طريق جائحة COVID-19 العالمية) . و توفر عقدة التصنيع (أو دقة تصنيع أياً كان المسمى المفضل لديك ) N5P كثافة ترانزستورات تقدر بنحو 171.3 مليون ترانزستور لكل ملم مربع ، مقارنة بـ 91.2 متر / ملم² التي كانت توفرها عملية تصنيع N7 .

الجدير بالذكر أيضاً أنه من المتوقع أن تكون شركة Apple هي أكبر عميل للعقدة الجديدة في عام 2020 ، حيث ستقوم الشركة ببناء سلسلة A14 من SoC عليها . مع مثل هذه الدقة في حيز التصنيع أتوقع أن نرى الجيل اللاحق من البطاقات الرسومية المبنية على معمارية AMD الجديدة (ما بعد RDNA 2) أو ما بعد معمارية NVIDA الجديدة Ampere ، أو الأجيال القادمة حتى من المعالجات المركزية على مثل هذه الدقة وهو ما سيوفر بكل تأكيد أداء أعلى بشكل ملحوظ للغاية مقارنة بالأجيال الحالية أو حتى الأجيال الجديدة التي سنراها (من المفترض) هذا العام في حال سارت الأمور على ما يرام .